# Triscend

### Triscend A7 Configurable System-on-Chip Platform

#### July, 2001 (Version 1.00)

#### Industry's first complete 32-bit Configurable System-on-Chip (CSoC)

- High-performance, low-power consumption, 32-bit RISC processor (ARM7TDMI™)

- 8K-byte mixed instruction/data cache

- 16K-byte internal scratchpad RAM

- Next-generation embedded programmable logic architecture (up to 40,000 gates)

- High-performance dedicated internal bus (up to 455M-bytes per second at 60 MHz)

- External memory interface supporting Flash, EEPROM, SRAM, and SDRAM

- Advanced real-time, in-system debugging capability

- Stand-alone operation from a single external memory (code + initialization)

- 2.5-volt core with 3.3- or 2.5-volt I/Os

- Four independent high-performance DMA channels

To external memory

#### Clock Synthesizer Selector PIO Memory Interface Únit **Power Control** PIO Selector SDRAM Controller Static/Flash Interface Selector PIO **Power-On Reset** Configurable PIO Selector System Logic Selector PIO (CSL) 16KBytes ScratchPad : PIO matrix ARM7TDMI SRAM Local CPU Bus PIO Selector or Trace Buffer Bus PIO Cache Data 8K Bytes **CSI Bridge** Bus Configurable System 4-way Set Associative Protection Unit Interconnect socket Address **Standard Peripherals** 16-input Hardware Interrupt Controller **Breakpoint Unit** 16-bit 16-bit Timer Timer Four-channel CSI Bus **DMA Controller** 32-bit Arbiter Watchdog Timer UART UART JTAG Interface with FIFO with **FIFO** Configurable System Interconnect (CSI) bus

#### **Product Description**

ARM

TCH305-0001-001

#### High-performance, 32-bit ARM7TDMI RISC Processor

- Best-selling 32-bit RISC processor

- Binary and source code compatible with other ARM7/ARM7TDMI variants

- Widespread C/C++ compiler, source-level debugger, and RTOS support

- Superior code density using the <u>Thumb</u><sup>®</sup> instruction set

- 54 MIPS (Dhrystone 2.1) at 60 MHz

- Low latency, real-time interrupt response

- Fast hardware multiplier

- 32-bit register bank and ALU

- 32-bit addressing 4G-byte linear address

- 32-bit barrel shifter

- EmbeddedICE™ on-chip debugger

| Device | Embedded<br>Processor<br>Core                             | Dedicated<br>Resources                                                                          | System<br>RAM | Configurable<br>System Logic<br>(CSL) Cells | CSI<br>Address<br>Selectors | PIO*<br>Pins<br>(Max) |

|--------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------|---------------------------------------------|-----------------------------|-----------------------|

| TA7S05 | ARM7TDMI                                                  | Two 16-bit timers<br>32-bit watchdog timer<br>16-input interrupt controller<br>Power management | 4Kx32         | 512                                         | 32                          | 124                   |

| TA7S12 | 32-bit RISC CPU<br>8K unified cache                       |                                                                                                 |               | 1,152                                       | 72                          | 188                   |

| TA7S20 | Barrel shifter<br>Hardware multiplier<br>Thumb extensions |                                                                                                 | 417.02        | 2,048                                       | 128                         | 252                   |

| TA7S32 | Debug extensions                                          | Hardware breakpoint unit<br>JTAG debugger                                                       |               | 3,200                                       | 200                         | 316                   |

#### Table 1. Triscend A7 Configurable System-on-Chip Family

\* Maximum PIO on each base device, actual PIO count depends on package style and initialization mode. See <u>Table 62</u>. Shaded entries are fabricated on 0.18µ CMOS.

#### Rich set of embedded support peripherals

- 4-channel high-performance DMA controller

- fly-by performance

- memory-to-memory transfers

- linked-list DMA

- frame transfer support

- Memory Subsystem Interface Unit (MSSIU) for flexible, glueless interface to external memories (ROM, EEPROM, Flash, SRAM, and SDRAM)

- Two 16C550-style serial ports (UART) with modem interface

- Two 16-bit timers/counters

- 32-bit Watchdog timer

- 16-input interrupt controller with fast interrupt response

- IEEE 1149.1 enhanced JTAG interface

- In-system debug/breakpoint unit

- Power-on reset

- Power-down and power-management modes

#### ■ Full-Featured Memory Interface Unit

- Simultaneous support for independent external Flash and SDRAM memory subsystems using x8 or x16 memory devices

- Expandable external data bus: 8-bit, 16-bit and 32-bit support

- Up to two external SDRAM banks

- Automatic support for self-refresh, autorefresh and initialization of SDRAM

- Programmable SDRAM parameters for optimal memory bandwidth

## Embedded SRAM-based Configurable System Logic (CSL) matrix

- Next-generation embedded programmable logic architecture, optimized with processor and bus interface

- Over 3,800 flip-flops and 300 programmable inputs and outputs (PIOs)

- Abundant, flexible interconnect structure with easy access to and from system bus

- Dedicated circuitry for fast adders, counters, and multipliers

- CSL cells optionally used as distributed memory, including true dual-port operation

- Six independent low-skew clock or global signal distribution buffers plus bus clock

- Supported by standard logic design tools

- VHDL and Verilog logic synthesis

- Schematic entry

- VHDL and Verilog simulation

#### High performance dedicated system bus

- Configurable System Interconnect (CSI) bus integrates CSL matrix, CSoC system

- 455M-bytes per second peak transfer rate

- 32-bit address bus and 32-bit data bus

- Programmable wait-state support

- Openly-defined CSI Socket bus interface to CSL matrix

- CSL peripheral addresses independent of placement in CSL matrix

- CSL peripherals compatible with past and future CSoC families

- Ten bus masters and built-in arbitration

- ARM7TDMI™ CPU

- Four-channel DMA controller

- JTAG interface

#### System Overview

The Triscend A7 Configurable System-on-Chip (CSoC) device is a complete, high-performance user-programmable system. The A7 contains

- an embedded 32-bit ARM7TDMI RISC processor

- a next generation embedded programmable logic architecture, optimized for processor and bus interface

- a high-performance 32-bit internal bus supporting up to 455M-bytes per second peak transfer rates

- 16K-bytes of internal scratchpad SRAM memory and a separate 8K-byte cache.

The ARM7TDMI is a general-purpose 32-bit RISC microprocessor that supports the complete ARM 32-bit instruction set and the reduced 16-bit instruction set, referred to as Thumb. The ARM7TDMI processor offers the following advantages:

- High-performance for very low power consumption and price

- Excellent code density using the Thumb instruction set

- Low-latency interrupt response

#### **ARM7TDMI Processor System with Cache, Scratchpad RAM**

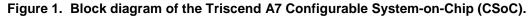

The processor is paired with an 8K-byte unified code/data cache and a 16K-byte (4Kx32) scratchpad RAM for storing timing critical code or data. The scratchpad is accessible over the Configurable System Interconnect (CSI) bus by other CSI bus masters, primarily for DMA transfers. The ARM processor is integrated with other system components and the Configurable System Logic (CSL) matrix to provide a complete configurable system, as illustrated in Figure 1.

#### Next-Generation Embedded Programmable Logic Architecture

The embedded SRAM-based Configurable System Logic (CSL) matrix provides full, easyto-use system customization. The high-performance programmable logic architecture consists of a highly interconnected matrix of CSL cells. Resources within the matrix provide seamless access to and from the internal CSI bus. Each CSL cell performs various potential functions, including combinatorial and sequential logic. The combinatorial portion performs Boolean logic operations, arithmetic functions, and memory. The sequential element performs independently or in tandem with the combinatorial function. The abundant programmable input/output blocks (PIOs) provide a highly flexible interface between external functions and the internal system bus or configurable system logic. Each PIO offers advanced I/O capabilities including selectable output drive current, optional input hysteresis, and programmable low-power functionality during power-down mode.

#### Internal, High-Performance Bus

A high-performance internal system bus—called the Configurable System Interconnect (CSI) bus— interconnects the embedded processor, its peripherals, and the CSL matrix at a maximum speed of 60MHz. The bus simultaneously provides 32 bits of read data, 32 bits of write data, and a 32-bit address. Multiple bus masters arbitrate for bus access. Potential bus masters include the ARM7TDMI processor, the read and write channels of all four DMA channels, and the JTAG interface. CSL-based devices become CSI bus masters using DMA services. The CSI bus and the local CPU bus following the little endian format.

Figure 2. A typical A7-based system.

#### External Interface to Flash, SDRAM

A static memory interface unit seamlessly connects the A7 device to external static memories such as Flash or SRAM, as shown in <u>Figure 2</u>. An external Flash memory device contains the A7's initialization boot program plus the system application code. The external memory interface has programmable read/write control and chip-select signals that provide flexible set-up, strobe, and hold timing. The CPU connects directly to external memory, eliminating any potential latency incurred by using the CSI bus. For low frequency or minimal applications, the ARM7TDMI processor directly fetches its instructions from external Flash.

The A7 optionally supports external SDRAM, offering additional affordable and highdensity memory to the system. The SDRAM interface connects an A7-based system to a variety of SDRAM types and configurations, including 100-pin DIMMs. The SDRAM interface operates at up to 60 MHz and provides options to optimize the interface timing for slower system clocks. SDRAM memory is ideal for DMA buffers. Similarly, the application program can be stored in slow, cheap, byte-wide Flash and copied into SDRAM at power-up. Then, the CPU starts executing code from the wider and faster SDRAM memory. The Flash and SDRAM interfaces share device pins, as shown in Figure 2.

#### **Four-Channel DMA**

The four-channel DMA controller provides high-bandwidth communication between CSLbased I/O devices, at up to 228M bytes per second, per direction. The easy-to-use DMA handshake simplifies interface and control logic within the CSL. The DMA controller provides advanced capabilities such as linked-list and frame-transfer support.

#### **Dedicated Peripherals**

The A7 also offers a set of common dedicated peripherals including

- two 16-bit timers with pre-scalers,

- two 16C450/550-like serial controllers (UART), with an optional modem interface

- a 32-bit watchdog timer, and

- an interrupt controller.

#### **Complete Single-Chip System**

The majority of the system, including the CPU, operates from a single clock signal. The clock source is typically driven directly via an external pin or connected to the on-chip PLL clock synthesizer. The clock synthesizer operates from an external 32.768 kHz watch crystal. Additionally, an internal ring oscillator is provided. Six other global buffers provide high-fanout signals to CSL functions. The bus clock and the global buffers are optionally stopped upon a breakpoint event and shut off during power-down mode.

Power management controls provide selectable power-down options over internal functions. Furthermore, each PIO provides pin-by-pin power-down settings.

An internal initialization boot ROM controls device initialization after power-on or after the reset pin is released. The initialization boot ROM locates user's initialization data and code stored in external Flash or other non-volatile memory. The Triscend FastChip development system programs external Flash via the A7's JTAG port.

Additionally, the JTAG interface provides real-time, in-system debugging capabilities, eliminating the need for an external emulator. The JTAG interface has full access and control over the CPU, peripherals, and CSL functions during debugging.

When debugging application software, the A7 employs the rich set of standard ARM7TDMI debugging tools. The A7 fully supports the standard ARM internal breakpoint and watchpoint capabilities. In addition, the A7's breakpoint unit monitors both the CPU local bus or the CSI bus. Upon a predefined set of conditions, the breakpoint unit halts or interrupts the execution of the application program. The breakpoint unit also supports real-time tracing of local CPU bus or the CSI bus transactions.

All together, the Triscend A7 Configurable System-on-Chip (CSoC) platform offers unparalleled time-to-market and performance advantages for embedded system designs.

#### A7 Development Support

The Triscend A7 Configurable System-on-Chip (CSoC) platform is supported by a variety of third-party development tools including compilers, debuggers, real-time operating systems (RTOS), and in-system debuggers/emulators as shown in <u>Table 2</u>. Most compilers that support the ARM7 architecture also support the Triscend A7 CSoC device. To accelerate development, there are multiple development boards available, shown in <u>Table 3</u>. Additionally, Triscend provides a free Software Development Kit (SDK) that includes board support packages (BSPs) for leading RTOS environments and a source-level driver library.

The A7's Configurable System Logic (CSL) matrix is well supported by a variety of logic design entry solutions, including both VHDL or Verilog logic synthesis and schematic entry as shown in <u>Table 2</u>. Likewise, there are VHDL and Verilog simulation models available for popular logic verification tools.

| Table 2. Supported Develo ARM7TDMI Software Development                                                                                                                                                                                                                           | CSoC/Logic Design Development                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Triscend Software Development Kit (SDK)                                                                                                                                                                                                                                           | Triscend <u>FastChip</u> CSoC Development<br>System                                                                                                                                                                                                                                                                                                                      |  |  |  |

| <ul> <li>Source-level device driver library</li> </ul>                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <ul> <li>Board Support Packages (BSPs)</li> </ul>                                                                                                                                                                                                                                 | <ul> <li>Graphical development/integration<br/>environment, Windows-based</li> </ul>                                                                                                                                                                                                                                                                                     |  |  |  |

| Compilers                                                                                                                                                                                                                                                                         | <ul> <li>Drag-and-drop <u>Soft Module</u> library</li> </ul>                                                                                                                                                                                                                                                                                                             |  |  |  |

| ■ Wind River <u>Diab C/C++™</u> Compiler                                                                                                                                                                                                                                          | <ul> <li>Create initialization images for Triscend</li> </ul>                                                                                                                                                                                                                                                                                                            |  |  |  |

| ARM <sup>®</sup> Developer Suite (ADS) C/C++                                                                                                                                                                                                                                      | CSoC devices                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Compiler                                                                                                                                                                                                                                                                          | <ul> <li>Download directly or program external</li> </ul>                                                                                                                                                                                                                                                                                                                |  |  |  |

| GNU C Compiler ( <u>GCC</u> )                                                                                                                                                                                                                                                     | Flash via JTAG                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Source-Level Debuggers                                                                                                                                                                                                                                                            | <ul> <li>Seamless integration with third-party</li> </ul>                                                                                                                                                                                                                                                                                                                |  |  |  |

| <ul> <li>Wind River <u>visionCLICK</u>, in-system sup-</li> </ul>                                                                                                                                                                                                                 | microprocessor and logic design tools                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| port using Wind River visionPROBE II                                                                                                                                                                                                                                              | <ul> <li>Powerful real-time, in-system debugging</li> </ul>                                                                                                                                                                                                                                                                                                              |  |  |  |

| <ul> <li>ARM eXtended Debugger (<u>AXD</u>)</li> </ul>                                                                                                                                                                                                                            | VHDL/Verilog Logic Synthesis                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| <ul> <li>GNU <u>gdb</u> Debugger</li> </ul>                                                                                                                                                                                                                                       | <ul> <li>Synplicity<sup>®</sup> Synplify<sup>®</sup></li> </ul>                                                                                                                                                                                                                                                                                                          |  |  |  |

| Real-Time Operating System (RTOS)                                                                                                                                                                                                                                                 | Synopsys <sup>®</sup> FPGA Compiler II                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Support                                                                                                                                                                                                                                                                           | Schematic Entry                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Wind River Tornado/ <u>VxWorks®</u>                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                                                                                                                                                                                                                                                   | Cadence/OrCAD Capture                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ■ Red Hat <u>eCos™</u>                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <ul> <li>Red Hat <u>eCos™</u></li> <li>Red Hat <u>µClinux</u></li> </ul>                                                                                                                                                                                                          | <ul> <li>SpinCircuit <u>eCapture</u></li> </ul>                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware</li> </ul>                                                                                                                                                                                                           | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> </ul>                                                                                                                                                                                                                                                                                        |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> </ul>                                                                                                                                                                                   | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> </ul>                                                                                                                                                                                                                                                         |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and</li> </ul>                                                                                                                                | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> </ul>                                                                                                                                                                                                              |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> </ul>                                                                                                            | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> </ul>                                                                                                                                                                    |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> </ul>                                                    | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> <li>VITAL/SDF support</li> </ul>                                                                                                                                         |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> <li>EPI JEENI and MAJIC<sup>™</sup> (ARM only</li> </ul> | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> <li>VITAL/SDF support</li> <li>Verilog Logic Simulation</li> </ul>                                                                                                       |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> </ul>                                                    | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> <li>VITAL/SDF support</li> <li>Verilog Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> </ul>                                                            |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> <li>EPI JEENI and MAJIC<sup>™</sup> (ARM only</li> </ul> | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> <li>VITAL/SDF support</li> <li>Verilog Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Cadence<sup>®</sup> <u>Verilog XL<sup>®</sup></u></li> </ul> |  |  |  |

| <ul> <li>Red Hat <u>µClinux</u></li> <li>JTAG-Based Hardware<br/>Emulators/Debuggers</li> <li>Wind River <u>visionPROBE II</u> (ARM and<br/>CSoC debugging)</li> <li>ARM Mutli-ICE<sup>™</sup> (ARM only debugging)</li> <li>EPI JEENI and MAJIC<sup>™</sup> (ARM only</li> </ul> | <ul> <li>SpinCircuit <u>eCapture</u></li> <li>Innoveda <u>ViewDraw</u></li> <li>VHDL Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> <li>Innoveda <u>Fusion/Speedwave</u></li> <li>VITAL/SDF support</li> <li>Verilog Logic Simulation</li> <li>Model Technology™ <u>ModelSim</u></li> </ul>                                                            |  |  |  |

#### Table 2. Supported Development Tools for A7 CSoC.

| Table 3. A7 Development Boards. |

|---------------------------------|

|---------------------------------|

| Supplier                        | Part Number        |

|---------------------------------|--------------------|

| Triscend Corporation            | <u>THW-KIT-720</u> |

| Embedded Performance Inc. (EPI) | Dev-A7             |

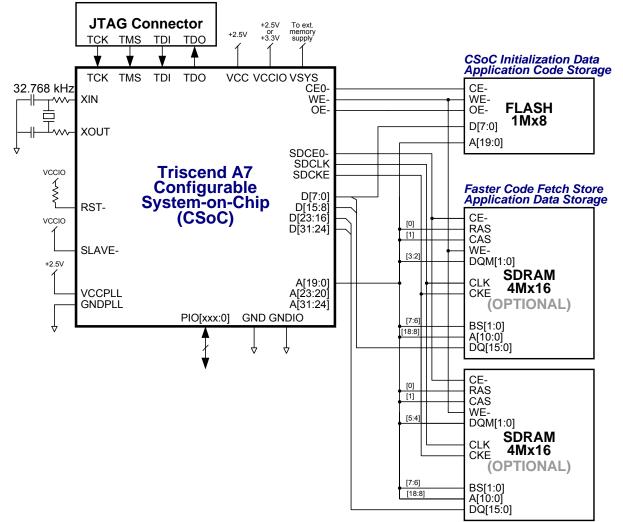

#### PC-Based Development Platform

<u>Figure 3</u> presents a detailed view of the entire Triscend A7 development flow. FastChip is a Windows-based application and operates on most PC-compatible computers with the recommended minimum 192M-bytes of RAM memory. The Triscend FastChip development system provides design integration and configuration capabilities, working in conjunction with third-party logic design and software development tools.

#### Powerful FastChip CSoC Development System

FastChip includes a powerful <u>Soft Module library</u> of commonly used embedded systems functions like additional UARTs, timers, various bus interfaces, etc. Likewise, FastChip includes libraries that allow designers to create custom functions using third-part logic design and simulation tools. Designs imported into FastChip via an EDIF 2.0.0 netlist become FastChip modules.

FastChip also exports a CSoC designs for either VHDL or Verilog logic simulation purposes. A Triscend-provided bus functional model simulates traffic on the A7's internal CSI bus.

#### Seamless Integration with ARM7TDMI Compiler

After defining the A7's logic, FastChip's Bind utility creates the physical hardware implementation for the CSoC device. Similarly, FastChip's Generate utility allocates addresses for any functions attached to the Configurable System Interconnect (CSI) bus and creates an application programming model for a third-party ARM compiler. This model includes register definitions for both standard ARM7TDMI functions and any custom hardware.

FastChip combines the output from the Bind utility and the object code from the ARM7TDMI compiler to create a CSoC initialization image. Using this image, FastChip either directly downloads to an A7 device or programs external Flash memory attached to the A7. Optionally, the initialization image can be saved as an Intel Hex file four use with an external device programmer.

#### Real-time, In-system, Full-Speed Debugging

Furthermore, FastChip provides a real-time, in-system debugging environment using the actual A7 production silicon with the actual system hardware and application software. FastChip drives a supported JTAG-based debugger/emulator and provides interfaces to third-party source-level debuggers. Via a source-level debugger, software developers have register-level access to the A7 device, complete with breakpoints and trace. FastChip's Debug utility also provides logic debugging capabilities, including the ability to probe flip-flop values and the outputs of CSL cells.

FastChip's Configure and Download/Debug utilities are packaged as a separate, standalone application called FastChip Device Link (FDL), providing software developers with necessary software development capabilities without the complexity of the entire FastChip CSoC development system.

#### **Comprehensive Technical Support**

The Triscend A7 Configurable System-on-Chip family and the FastChip development system are supported by a world-wide network of factory-trained field applications engineers. Additionally, the Triscend SupportCenter provides online support via the world-wide web at <a href="http://support.triscend.com">http://support.triscend.com</a> or via E-mail at <a href="http://supportCenter@Triscend.com">SupportCenter@Triscend.com</a>.

#### Resources

#### Web Sites

#### **ARM7TDMI** Information

www.arm.com

ARM Development Guide

www.embedded.com/directories/embedded/arm2000/index.html

**ARM Resources Links**

www.bluewaternz.com/links.htm

#### **Books**

#### ARM Architecture Reference Manual

D. Jaggar, David Seal Prentice Hall: ISBN 0201737191

#### ARM System-on-Chip Architecture (Second Edition)

S. Furber Addison-Wesley: ISBN 0201675196

#### ARM System Architecture

S. Furber Addison-Wesley: ISBN 0201403528

Japanese translation available: Book title: ARM Processor Publishing company: CQ Publishing Co., Ltd. ISBN 4789833518

#### The ARM RISC Chip, A Programmer's Guide

A. van Someron and C. Atack Addison-Wesley: ISBN 0201624109

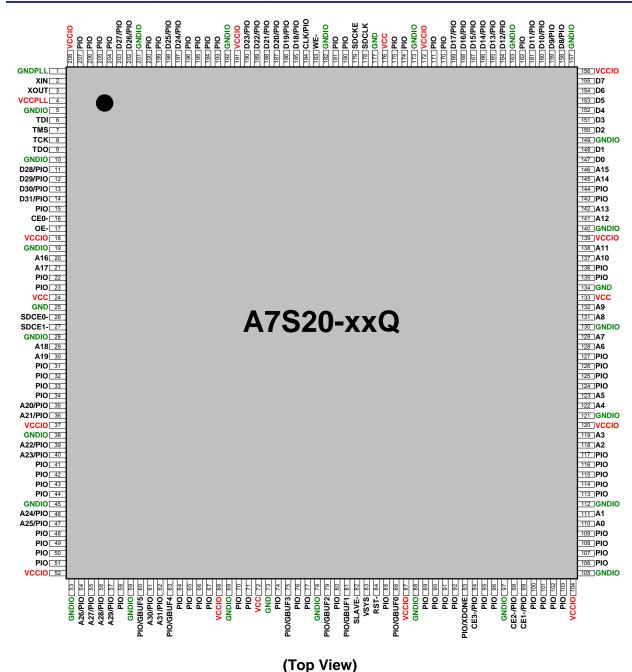

#### **Pin Description**

<u>Table 60</u> describes the pins available on an A7 configurable system-on-chip (CSoC) device. The directionality of each pin is described during parallel mode initialization. After initialization, all PIO pins and the indicated system pins are available as user-defined I/O signals.

|                                                                            | 0. Pins available on an A7 configurable system-on-chip and their                                                                                                                                                                                                                                                                                                                                                                                                 | function.      |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Pin Name                                                                   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Parallel       |

| A[19:0]                                                                    | Address bus bits. These pins cannot be reclaimed as user-defined PIO pins.                                                                                                                                                                                                                                                                                                                                                                                       | 0              |

| CE0-                                                                       | Active-Low chip-enable output to external memory. Enables all bytes in an 8-bit subsystem, or the first byte of a 16-bit or 32-bit subsystem, or the first half-word of a 32-bit subsystem using 16-bit wide memories. This pin cannot be reclaimed as a user-defined PIO pin.                                                                                                                                                                                   | 0              |

| CE[3:1]-<br>/PIO                                                           | Optional active-Low byte-lane chip-enable signals. Used to enable external memory during byte or half-word addressing in 16-bit or 32-bit Flash memory subsystems. If not used as chip-enables, these pins may be reclaimed as user-defined PIO pins.                                                                                                                                                                                                            | Ο              |

| CLK/PIO                                                                    | External clock source input. Can be reclaimed as a PIO pin if not used as the system clock source.                                                                                                                                                                                                                                                                                                                                                               | Ι              |

| D[7:0]                                                                     | Data bus bits. These pins cannot be reclaimed as user-defined PIO pins.                                                                                                                                                                                                                                                                                                                                                                                          |                |

| DQ[31:8]                                                                   | Optional upper 24 bits of the Data bus. These pins may be reclaimed as user-defined PIO pins. Until initialization is complete, these pins have an internal high-impedance pull-up resistor.                                                                                                                                                                                                                                                                     | I              |

| GND                                                                        | Ground connection for internal (non-PIO) logic. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                           |                |

| GNDIO                                                                      | Ground connection for PIO functions. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| GNDPLL                                                                     | Ground connection for the phase-locked loop (PLL). Must be connected.                                                                                                                                                                                                                                                                                                                                                                                            |                |

| N.C.                                                                       | No connect. There is no function on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                    | N.C.           |

| OE-                                                                        | Active-Low output-enable signal to read from external memory.                                                                                                                                                                                                                                                                                                                                                                                                    | 0              |

| PIO                                                                        | General-purpose input, output, or bi-directional signal pin after initialization<br>is complete. Before initialization is complete, these pins have internal high-<br>impedance pull-up resistors that pull the signal pin to a High logic level.                                                                                                                                                                                                                | l<br>(pull-up) |

| PIO/<br>A[23:20]                                                           | Typically, a general-purpose input, output, or bi-directional signal pin after<br>initialization is complete. Before initialization is complete, these pins have<br>an internal high-impedance pull-up resistor that pulls the signal pin to a<br>High logic level.<br>These pins optionally extend the Flash subsystem address up to the maxi-<br>mum 16M-bytes allowed after initialization. Any unused address lines may<br>be used as user-defined PIO pins. | l<br>(pull-up) |

| PIO/<br>A[31:24]                                                           | Typically, a general-purpose input, output, or bi-directional signal pin after<br>initialization is complete. Before initialization is complete, these pins have<br>an internal high-impedance pull-up resistor that pulls the signal pin to a<br>High logic level.<br>These pins are optionally used as the upper 8-bit of the 32-bit CSI bus ad-<br>dress during testing.                                                                                      | l<br>(pull-up) |

| PIO/GBUF5<br>PIO/GBUF4<br>PIO/GBUF3<br>PIO/GBUF2<br>PIO/GBUF1<br>PIO/GBUF0 | Global buffer input. Typically, a general-purpose input, output, or bi-<br>directional signal pin after initialization is complete. Before initialization is<br>complete, this pin has an internal high-impedance pull-up resistor that pulls<br>the signal pin to a High logic level.                                                                                                                                                                           | l<br>(pull-up) |

#### Table 60. Pins available on an A7 configurable system-on-chip and their function.

| Pin Name   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Parallel  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|            | General-purpose input, output, or bi-directional signal pin after initialization                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| PIO/XDONE  | is complete. Before initialization is complete, this pin has an internal high-                                                                                                                                                                                                                                                                                                                                                                                                                                        | I         |

| FIO/ADONE  | impedance pull-up resistor that pulls the signal pin to a High logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                           | (pull-up) |

|            | This pin is optionally used during testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| RST-       | Active-Low device reset input. Connect to VCCIO with a pull-up resistor. Do not allow it to float.                                                                                                                                                                                                                                                                                                                                                                                                                    | Ι         |

| SDCE[1:0]- | Active-Low SDRAM chip-enable signals. If not used, leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0         |

| SDCKE      | SDRAM clock enable signal. Disables SDRAM during power-down condi-<br>tions. If not used, leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                          | 0         |

| SDCLK      | SDRAM clock source. All SDRAM operations are synchronized to the rising edge of this signal. If not used, leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                          | 0         |

| SLAVE-     | Test slave mode. Connect to VCCIO. Do not allow it to float.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -         |

| TCK        | JTAG Test Clock input. Tie High if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I         |

| TDI        | JTAG Test Data Input. Tie High if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | l         |

| TDO        | JTAG Test Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0         |

| TMS        | JTAG Test Mode Select input. Tie High if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| VCC        | Supply voltage for internal logic functions, separate from I/O. Connect to a +2.5-volt supply. DO NOT CONNECT TO +3.3-VOLT SUPPLY. All must be connected and each must be decoupled with a 0.01 to 0.1 $\mu$ F capacitor to ground.                                                                                                                                                                                                                                                                                   | Ι         |

| VCCIO      | Supply voltage for I/O functions, separate from internal logic. Connect all to a +2.5-volt or +3.3-volt supply, depending on external interface requirements. All must be connected and each must be decoupled with a 0.01 to 0.1 $\mu$ F capacitor to ground.                                                                                                                                                                                                                                                        | I         |

| VCCPLL     | Supply voltage for phase-locked loop circuitry. Connect to a +2.5-volt supply. Must be connected and decoupled with a 0.01 to 0.1 $\mu$ F capacitor to ground.                                                                                                                                                                                                                                                                                                                                                        | I         |

| VSYS       | External 'system voltage-good' indicator input. Indicates when external devices, such as the external Flash, have sufficient operating voltage. In most applications, connect VSYS to VCCIO supply source. If VSYS is High during initialization and no valid configuration is found, the CSoC device automatically powers down to conserve power. If VSYS is tied Low, the CSoC device attempts to initialize itself until it finds valid initialization data. This pin must be connected. Do not allow it to float. | I         |

| WE-        | Active-Low write-enable signal to write to external memory. Used to pro-<br>gram external Flash-based devices.                                                                                                                                                                                                                                                                                                                                                                                                        | 0         |

| XIN        | The input from an external 32.768 kHz watch crystal into the internal crystal oscillator amplifier. Connect to one side of the external crystal as shown in <u>Figure 47</u> . Connect to GNDIO if not using an external crystal.                                                                                                                                                                                                                                                                                     | I         |

| XOUT       | Output from the 32.768 kHz internal crystal oscillator amplifier. Connect to one side of the external Hz watch crystal. Leave unconnected if not using an external crystal.                                                                                                                                                                                                                                                                                                                                           | I/O       |

#### 208-pin PQFP Package Footprint Diagram

|   |             |             |             | -           |               | •           |             |               |               |               |               |             |             |             |               |               |              |     |

|---|-------------|-------------|-------------|-------------|---------------|-------------|-------------|---------------|---------------|---------------|---------------|-------------|-------------|-------------|---------------|---------------|--------------|-----|

|   | 1           | 2           | 3           | 4           | 5             | 6           | 7           | 8             | 9             | 10            | 11            | 12          | 13          | 14          | 15            | 16            | 17           | 18  |

| A | GND<br>PLL  | PIO         | PIO         | D22/<br>PIO | D21/<br>PIO   | D20/<br>PIO | D19/<br>PIO | WE-           | SD<br>CKE     | SD<br>CLK     | D17/<br>PIO   | D15/<br>PIO | D13/<br>PIO | D11/<br>PIO | D10/<br>PIO   | D9/<br>PIO    | D8/<br>PIO   | D5  |

| в | XIN         | D25/<br>PIO | PIO         | D27/<br>PIO | D26/<br>PIO   | D24/<br>PIO | D23/<br>PIO | D18/<br>PIO   | CLK/<br>PIO   | PIO           | D16/<br>PIO   | D14/<br>PIO | D12/<br>PIO | PIO         | PIO           | PIO           | D7           | D3  |

| с | хоит        | TDI         | PIO         | PIO         | PIO           | PIO         | PIO         | PIO           | PIO           | PIO           | PIO           | PIO         | PIO         | PIO         | PIO           | PIO           | D6           | D2  |

| D | VCC<br>PLL  | тмз         | PIO         | PIO         | PIO           | PIO         | PIO         | PIO           | PIO           | PIO           | PIO           | PIO         | PIO         | PIO         | PIO           | PIO           | D4           | D1  |

| E | GNDIO       | тск         | PIO         | PIO         | vccio         | vccio       | vccio       | PIO           | PIO           | PIO           | PIO           | vccio       | vccio       | vccio       | PIO           | PIO           | D0           | A14 |

| F | D28/<br>PIO | TDO         | PIO         | PIO         | vccio         | VCCIO       | GNDIO       | GNDIO         | vcc           | GND           | GNDIO         | GNDIO       | vccio       | vccio       | PIO           | PIO           | A15          | PIO |

| G | D30/<br>PIO | D29/<br>PIO | PIO         | PIO         | vccio         | GNDIO       | GNDIO       | GNDIO         | vcc           | GND           | GNDIO         | GNDIO       | GNDIO       | vccio       | PIO           | PIO           | PIO          | PIO |

| н | CE0-        | D31/<br>PIO | PIO         | PIO         | PIO           | GNDIO       | GNDIO       | GNDIO         | GNDIO         | GNDIO         | GNDIO         | GNDIO       | GNDIO       | PIO         | PIO           | PIO           | PIO          | A12 |

| J | A16         | OE-         | PIO         | PIO         | PIO           | VCC         | vcc         | GNDIO         | GNDIO         | GNDIO         | GNDIO         | GND         | GND         | PIO         | PIO           | PIO           | A8           | A10 |

| к | A17         | PIO         | PIO         | PIO         | PIO           | GND         | GND         | GNDIO         | GNDIO         | GNDIO         | GNDIO         | vcc         | vcc         | PIO         | PIO           | PIO           | A6           | A13 |

| L | SD<br>CE0-  | PIO         | PIO         | PIO         | PIO           | GNDIO       | GNDIO       | GNDIO         | GNDIO         | GNDIO         | GNDIO         | GNDIO       | GNDIO       | PIO         | PIO           | PIO           | PIO          | A11 |

| м | SD<br>CE1-  | PIO         | PIO         | PIO         | vccio         | GNDIO       | GNDIO       | GNDIO         | vcc           | GND           | GNDIO         | GNDIO       | GNDIO       | vccio       | PIO           | PIO           | PIO          | A9  |

| N | A18         | A20/<br>PIO | PIO         | PIO         | vccio         | vccio       | GNDIO       | GNDIO         | vcc           | GND           | GNDIO         | GNDIO       | vccio       | vccio       | PIO           | PIO           | A4           | A7  |

| Р | PIO         | A19         | PIO         | PIO         | vccio         | vccio       | vccio       | PIO           | PIO           | PIO           | PIO           | VCCIO       | VCCIO       | vccio       | PIO           | PIO           | PIO          | A5  |

| R | A22/<br>PIO | A21/<br>PIO | PIO         | PIO         | PIO           | PIO         | PIO         | PIO           | PIO           | PIO           | PIO           | PIO         | PIO         | PIO         | PIO           | PIO           | PIO          | A3  |

| т | A23/<br>PIO | PIO         | PIO         | PIO         | PIO           | PIO         | PIO         | PIO           | PIO           | PIO           | PIO           | PIO         | PIO         | PIO         | PIO           | PIO           | PIO          | A2  |

| U | A24/<br>PIO | A26/<br>PIO | PIO         | PIO         | PIO           | PIO         | PIO         | PIO           | PIO           | PIO           | PIO           | PIO         | PIO         | PIO         | PIO           | PIO/<br>XDONE | CE2-/<br>PIO | A1  |

| v | A25/<br>PIO | A27/<br>PIO | A28/<br>PIO | A29/<br>PIO | PIO/<br>GBUF5 | A30/<br>PIO | A31/<br>PIO | PIO/<br>GBUF4 | PIO/<br>GBUF3 | PIO/<br>GBUF2 | PIO/<br>GBUF1 | SLAVE-      | VSYS        | RST-        | PIO/<br>GBUF0 | CE3-/<br>PIO  | CE1-/<br>PIO | A0  |

#### 324-ball BGA Package Footprint Diagram

(Top view, through top of package to solder balls underneath)

#### **Electrical and Timing Characteristics**

#### Absolute Maximum Ratings

| Symbol           | Parameter                                 | Min  | Max  | Units |

|------------------|-------------------------------------------|------|------|-------|

| Vcc              | Core logic supply voltage relative to GND | -0.5 | 3.0  | V     |

| Vccio            | PIO supply voltage relative to GND        | -0.5 | 4.0  | V     |

| VIN              | Input voltage relative to GND [1]         | -0.5 | 4.0  | V     |

| V <sub>TS</sub>  | Voltage applied to three-state output [1] | -0.5 | 4.0  | V     |

| T <sub>STG</sub> | Storage temperature (ambient)             | -60  | +150 | °C    |

| T <sub>SOL</sub> |                                           |      | +260 | °C    |

| TJ               | Junction temperature, plastic packages    |      | +125 | °C    |

#### **Recommended Operating Conditions/DC Characteristics**

| Symbol            | Parameter                                                                   | Min                 | Max                  | Units |

|-------------------|-----------------------------------------------------------------------------|---------------------|----------------------|-------|

| Vcc               | Core logic supply voltage relative to GND                                   | 2.3                 | 2.7                  | V     |

| V <sub>CCIO</sub> | PIO supply voltage relative to GND                                          | 2.3                 | 3.6                  | V     |

|                   | Operating junction temperature, commercial [3]                              | 0                   | +85                  | °C    |

| TJ                | Operating junction temperature, industrial [3]                              | -40                 | +100                 | °C    |

| V <sub>CCR</sub>  | Longest supply voltage rise time from 1V to 3V [4]                          |                     | 200                  | ms    |

| VIL               | Input Low voltage                                                           | 0                   | 30% V <sub>CC</sub>  | V     |

| VIH               | Input High voltage                                                          | 50% V <sub>CC</sub> | V <sub>CC</sub> +0.5 | V     |

| Vs                | Schmitt Hysteresis, hysteresis mode                                         | 5% VCC              | 20% VCC              | V     |

| V <sub>ESD</sub>  | Electro-static discharge protection, human body model                       | 2 000               |                      | V     |

| T <sub>IN</sub>   | Input signal transition time                                                |                     | 250                  | ns    |

| V                 | Output Low voltage, $I_{OL}$ = -16 mA, $V_{CC}$ min (TTL) [5]               |                     | 0.4                  | V     |

| V <sub>OL</sub>   | Output Low voltage, I <sub>OL</sub> = -1.5 mA, V <sub>CC</sub> min (LVCMOS) |                     | 10% VCC              | V     |

| V                 | Output High voltage, $I_{OH}$ = 8 mA, $V_{CC}$ min (TTL) [5]                | 2.4                 |                      | V     |

| V <sub>OH</sub>   | Output High voltage, $I_{OH}$ = 0.5 mA, $V_{CC}$ min (LVCMOS)               | 90% VCC             |                      | V     |

| V <sub>DR</sub>   | Data retention supply voltage of internal core logic (below                 | 2.5                 |                      | V     |

| V DR              | which initialization data may be lost)                                      | 2.5                 |                      | v     |

| V <sub>DRIO</sub> | Data retention supply voltage of PIO (below which initializa-               | 2.1                 |                      | V     |

| V DRIU            | tion data may be lost)                                                      | 2.1                 |                      | v     |

|                   | Output Low current, output in highest drive strength mode                   |                     | -16.0                | mA    |

|                   | (TTL), V <sub>OL</sub> max, V <sub>CC</sub> min                             |                     | 10.0                 |       |

| I <sub>OL</sub>   | Output Low current, output in lowest current drive mode                     |                     | -4.0                 | mA    |

|                   | (TTL), V <sub>OL</sub> max, V <sub>CC</sub> min                             |                     |                      |       |

|                   | Output Low current (LVCMOS), V <sub>OL</sub> max, V <sub>CC</sub> min       |                     | -1.5                 | mA    |

|                   | Output High current, output in highest drive strength mode                  |                     | +8.0                 | mA    |

|                   | (TTL), V <sub>OH</sub> min, V <sub>CC</sub> min                             | -                   |                      |       |

| I <sub>OH</sub>   | Output High current, output in lowest drive strength mode                   |                     | +2.0                 | mA    |

|                   | (TTL), V <sub>OH</sub> min, V <sub>CC</sub> min                             |                     | 10.5                 | 100 A |

| <b></b>           | Output High current (LVCMOS), V <sub>OH</sub> min, V <sub>CC</sub> min      | -10                 | +0.5                 | mA    |

| l⊫                | Input leakage current                                                       | -10                 | +10                  | μA    |

| CIO               | Pin capacitance [7]                                                         |                     | 10                   | pF    |

| L <sub>IO</sub>   | Pin inductance [7]                                                          |                     | 20                   | nH    |

**Note 1:** Maximum DC overshoot above VCC or undershoot below GND must be limited to either 0.5 V or 10 mA, whichever is easier to achieve. During transitions, device pins may undershoot to -2.0 V or overshoot to +5.0 V, provided this condition lasts less than 20 ns and with less than 100 mA forcing current.

**Note 2:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent device damage. The values listed are stress ratings only. Functional operation of the device at these or any conditions exceeding those listed under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods may affect device reliability.

**Note 3:** Typical ambient operating conditions are between 0 to +70° C for commercial devices and -40 to +85° C for industrial devices, depending on the application's power consumption, package style, and airflow.

Note 4: Ramp rate can be extended by asserting RST- until V<sub>CC</sub> reaches the minimum specified value.

**Note 5:** Output in highest drive strength mode.

**Note 6:** Continuous static loads must fall within the I<sub>OH</sub>, I<sub>OL</sub> limits in this section.

**Note 7:** Capacitance and inductance is sample-tested only.

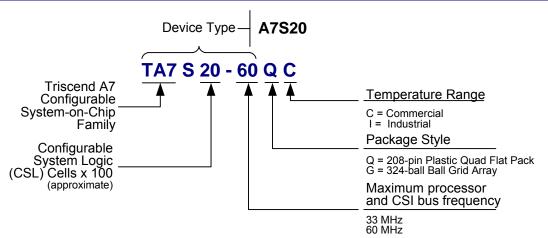

#### Ordering Information

tive in your area.

Web: www.triscend.com

| Sales Offices                                                  |                                                               |                                                                      |  |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Headquarters                                                   | U.S. Distribution                                             | Asia-Pacific<br>Unique Asia Pacific<br>Web: <u>www.unique-ap.com</u> |  |  |  |  |  |

| Triscend Corporation<br>301 North Whisman Road                 | All American Semiconductor<br>Web: <u>www.allamerican.com</u> |                                                                      |  |  |  |  |  |

| Mountain View, CA 94043<br>USA                                 | Unique Technologies                                           | Japan                                                                |  |  |  |  |  |

| Tel: 1-650-968-8668                                            | Web:<br>www.unique-technologies.com                           | Internix Incorporated                                                |  |  |  |  |  |

| Fax: 1-650-934-9393                                            | Europe, Middle-East, South                                    | Tel: <b>(03) 3369-1101</b><br>Fax: (03) 3366-8566                    |  |  |  |  |  |

| Sales Representatives                                          | Africa                                                        | Web: www.internix.co.jp                                              |  |  |  |  |  |

| Visit the Triscend web site for the Triscend sales representa- | <b>Unique</b><br>Web: <u>www.unique.memec.com</u>             |                                                                      |  |  |  |  |  |

301 N. Whisman Rd. Mountain View, CA 94043-3969 Tel: 1-650-968-8668 Fax: 1-650-934-9393 E-mail: <u>supportCenter@Triscend.com</u> Web: www.triscend.com

Triscend, the Triscend logo, and FastChip ™ are trademarks of Triscend Corporation. All other trademarks are the property of their respective owners.

Triscend Corporation does not assume liability resulting from the application or use of any product described herein. No circuit patent licenses are implied. Triscend Corporation reserves the right to make changes without notice to any product herein to improve reliability, function, or design. U.S. and international patents pending.