# 82C288 BUS CONTROLLER FOR 80286 PROCESSORS (82C288-12, 82C288-10, 82C288-8)

- Provides Commands and Controls for Local and System Bus

- Wide Flexibility in System Configurations

- High Speed CHMOS III Technology

- Fully Static Device

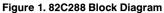

- Available in 20 Pin PLCC (Plastic Leaded Chip Carrier) and 20 Pin Cerdip Packages

(See Packaging Spec, Order #231369)

■ Fully Compatible with the HMOS 82288

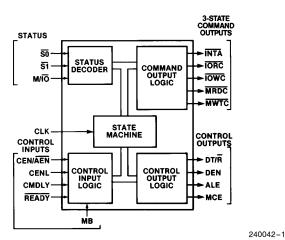

The Intel 82C288 Bus Controller is a 20-pin CHMOS III component for use in 80286 microsystems. The 82C288 is fully compatible with its predecessor the HMOS 82288. The bus controller is fully static and supports a low power mode. The bus controller provides command and control outputs with flexible timing options. Separate command outputs are used for memory and I/O devices. The data bus is controlled with separate data enable and direction control signals.

Two modes of operation are possible via a strapping option: MULTIBUS I compatible bus cycles, and high speed bus cycles.

September 1989

Order Number: 240042-003

Figure 2. 82C288 Pin Configuration

int<sub>el</sub>.

### Table 1. Pin Description

The following pin function descriptions are for the 82C288 bus controller.

| Symbol        | Туре |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        | Name and Function                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|---------------|------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| CLK           | I    | micros<br>edge c                                  | <b>SYSTEM CLOCK</b> provides the basic timing control for the 82C288 in an 80286 microsystem. Its frequency is twice the internal processor clock frequency. The falling edge of this input signal establishes when inputs are sampled and command and control outputs change.                                                                                                                                                                                                                                                                                                                         |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| <u>50, 51</u> | I    | cycle.<br>sample                                  | <b>BUS CYCLE STATUS</b> starts a bus cycle and, along with $M/\overline{IO}$ , defines the type of bus cycle. These inputs are active LOW. A bus cycle is started when either $\overline{S1}$ or $\overline{S0}$ is sampled LOW at the falling edge of CLK. Setup and hold times must be met for proper operation.                                                                                                                                                                                                                                                                                     |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|               |      |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        | 80286 Bus Cycle Status Definition                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|               |      | M/IO                                              | <u>S1</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S0                     | Type of Bus Cycle                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|               |      | 0                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                      | Interrupt Acknowledge                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|               |      | 0                                                 | 0 0 1 1/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|               |      | 0                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                      | I/O Write<br>None; Idle                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|               |      | 1                                                 | o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                      | Halt or Shutdown                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|               |      | 1                                                 | Ö                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                      | Memory Read                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|               |      | 1                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                      | Memory Write                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|               |      | 1                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                      | None; Idle                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| M/ĪŌ          | I    | space                                             | <b>MEMORY OR I/O SELECT</b> determines whether the current bus cycle is in the memory space or I/O space. When LOW, the current bus cycle is in the I/O space. Setup and hold times must be met for proper operation.                                                                                                                                                                                                                                                                                                                                                                                  |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| MB            | I    | When<br>LOW, to<br>cycles.                        | <b>MULTIBUS MODE SELECT</b> determines timing of the command and control outputs.<br>When HIGH, the bus controller operates with MULTIBUS I compatible timings. When<br>LOW, the bus controller optimizes the command and control output timing for short bus<br>cycles. The function of the CEN/AEN input pin is selected by this signal. This input is<br>typically a strapping option and not dynamically changed.                                                                                                                                                                                  |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| CENL          | I    | control<br>input la<br>approp<br>one bu           | <b>COMMAND ENABLE LATCHED</b> is a bus controller select signal which enables the bus controller to respond to the current bus cycle being initiated. CENL is an active HIGH input latched internally at the end of each $T_S$ cycle. CENL is used to select the appropriate bus controller for each bus cycle in a system where the CPU has more than one bus it can use. This input may be connected to $V_{CC}$ to select this 82C288 for all transfers. No control inputs affect CENL. Setup and hold times must be met for proper                                                                 |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| CMDLY         | Ι    | input. I<br>sample<br>READ<br>termina<br>satisfie | <b>COMMAND DELAY</b> allows delaying the start of a command. CMDLY is an active HIGH input. If sampled HIGH, the command output is not activated and CMDLY is again sampled at the next CLK cycle. When sampled LOW the selected command is enabled. If READY is detected LOW before the command output is activated, the 82C288 will terminate the bus cycle, even if no command was issued. Setup and hold times must be satisfied for proper operation. This input may be connected to GND if no delays are required before starting a command. This input has no effect on 82C288 control outputs. |                        |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| READY         | I    | MULTI<br>becom                                    | BUS<br>ie act<br>Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l moc<br>ive. F<br>and | The end of the current bus cycle. $\overline{\text{READY}}$ is an active LOW input.<br>The requires at least one wait state to allow the command outputs to<br>$\overline{\text{READY}}$ must be LOW during reset, to force the 82C288 into the idle<br>hold times must be met for proper operation. The 82C284 drives $\overline{\text{READY}}$<br>ET. |  |  |  |  |  |  |  |  |  |

### Table 1. Pin Description (Continued)

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CEN/AEN |      | <b>COMMAND ENABLE/ADDRESS ENABLE</b> controls the command and DEN outputs of the bus controller. CEN/AEN inputs may be asynchronous to CLK. Setup and hold times are given to assure a guaranteed response to synchronous inputs. This input may be connected to $V_{CC}$ or GND.                                                                                                                                                                                                                                                                                                                                                                            |

|         |      | When MB is HIGH this pin has the AEN function. AEN is an active LOW input<br>which indicates that the CPU has been granted use of a shared bus and the<br>bus contoller command outputs may exit 3-state OFF and become inactive<br>(HIGH). AEN HIGH indicates that the CPU does not have control of the shared<br>bus and forces the command outputs into 3-state OFF and DEN inactive<br>(LOW).                                                                                                                                                                                                                                                            |

|         |      | When MB is LOW this pin has the CEN function. CEN is an unlatched active HIGH input which allows the bus controller to activate its command and DEN outputs. With MB LOW, CEN LOW forces the command and DEN outputs inactive but does not tristate them.                                                                                                                                                                                                                                                                                                                                                                                                    |

| ALE     | 0    | ADDRESS LATCH ENABLE controls the address latches used to hold an address stable during a bus cycle. This control output is active HIGH. ALE will not be issued for the halt bus cycle and is not affected by any of the control inputs.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCE     | 0    | MASTER CASCADE ENABLE signals that a cascade address from a master<br>8259A interrupt controller may be placed onto the CPU address bus for<br>latching by the address latches under ALE control. The CPU's address bus<br>may then be used to broadcast the cascade address to slave interrupt<br>controllers so only one of them will respond to the interrupt acknowledge cycle.<br>This control output is active HIGH. MCE is only active during interrupt<br>acknowledge cycles and is not affected by any control input. Using MCE to<br>enable cascade address drivers requires latches which save the cascade<br>address on the falling edge of ALE. |

| DEN     | 0    | <b>DATA ENABLE</b> controls when data transceivers connected to the local data bus should be enabled. DEN is an active HIGH control output. DEN is delayed for write cycles in the MULTIBUS I mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DT/R    | 0    | <b>DATA TRANSMIT/RECEIVE</b> establishes the direction of data flow to or from the local data bus. When HIGH, this control output indicates that a write bus cycle is being performed. A LOW indicates a read bus cycle. DEN is always inactive when $DT/\overline{R}$ changes states. This output is HIGH when no bus cycle is active. $DT/\overline{R}$ is not affected by any of the control inputs.                                                                                                                                                                                                                                                      |

| IOWC    | 0    | I/O WRITE COMMAND instructs an I/O device to read the data on the data<br>bus. This command output is active LOW. The MB and CMDLY inputs control<br>when this output becomes active. READY controls when it becomes inactive.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IORC    | 0    | I/O READ COMMAND instructs an I/O device to place data onto the data bus.<br>This command output is active LOW. The MB and CMDLY inputs control when<br>this output becomes active. READY controls when it becomes inactive.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MWTC    | 0    | <b>MEMORY WRITE COMMAND</b> instructs a memory device to read the data on<br>the data bus. This command output is active LOW. The MB and CMDLY inputs<br>control when this output becomes active. READY controls when it becomes<br>inactive.                                                                                                                                                                                                                                                                                                                                                                                                                |

| MRDC    | 0    | <b>MEMORY READ COMMAND</b> instructs the memory device to place data onto<br>the data bus. This command output is active LOW. The MB and CMDLY inputs<br>control when this output becomes active. READY controls when it becomes<br>inactive.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table | 1 Pin   | Descri | ntion ( | (Continued) |

|-------|---------|--------|---------|-------------|

| Iable | 1. FIII | Descil |         | Continueu)  |

| Symbol          | Туре | Name and Function                                                                                                                                                                                                                                        |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĪNTĀ            | 0    | <b>INTERRUPT ACKNOWLEDGE</b> tells an interrupting device that its interrupt request is being acknowledged. This command output is active LOW. The MB and CMDLY inputs control when this output becomes active. READY controls when it becomes inactive. |

| V <sub>CC</sub> |      | System Power: +5V Power Supply                                                                                                                                                                                                                           |

| GND             |      | System Ground: 0V                                                                                                                                                                                                                                        |

#### Table 2. Command and Control Outputs for Each Type of Bus Cycle

| Type of<br>Bus Cycle  | M/IO | <u>S1</u> | <del>S0</del> | Command<br>Activated | DT/ <del>R</del><br>State | ALE, DEN<br>Issued? | MCE<br>Issued? |

|-----------------------|------|-----------|---------------|----------------------|---------------------------|---------------------|----------------|

| Interrupt Acknowledge | 0    | 0         | 0             | INTA                 | LOW                       | YES                 | YES            |

| I/O Read              | 0    | 0         | 1             | IORC                 | LOW                       | YES                 | NO             |

| I/O Write             | 0    | 1         | 0             | IOWC                 | HIGH                      | YES                 | NO             |

| None; Idle            | 0    | 1         | 1             | None                 | HIGH                      | NO                  | NO             |

| Halt/Shutdown         | 1    | 0         | 0             | None                 | HIGH                      | NO                  | NO             |

| Memory Read           | 1    | 0         | 1             | MRDC                 | LOW                       | YES                 | NO             |

| Memory Write          | 1    | 1         | 0             | MWTC                 | HIGH                      | YES                 | NO             |

| None; Idle            | 1    | 1         | 1             | None                 | HIGH                      | NO                  | NO             |

### **Operating Modes**

Two types of buses are supported by the 82C288: MULTIBUS I and non-MULTIBUS I. When the MB input is strapped HIGH, MULTIBUS I timing is used. In MULTIBUS I mode, the 82C288 delays command and data activation to meet IEEE-796 requirements on address to command active and write data to command active setup timing. MULTIBUS I mode requires at least one wait state in the bus cycle since the command outputs are delayed. The non-MULTIBUS I mode does not delay any outputs and does not require wait states. The MB input affects the timing of the command and DEN outputs.

### **Command and Control Outputs**

The type of bus cycle performed by the local bus master is encoded in the  $M/\overline{IO}$ ,  $\overline{S1}$ , and  $\overline{S0}$  inputs. Different command and control outputs are activated depending on the type of bus cycle. Table 2 indicates the cycle decode done by the 82C288 and the effect on command, DT/ $\overline{R}$ , ALE, DEN, and MCE outputs.

Bus cycles come in three forms: read, write, and halt. Read bus cycles include memory read, I/O read, and interrupt acknowledge. The timing of the associated read command outputs (MRDC, IORC,

and  $\overline{\text{INTA}}$ , control outputs (ALE, DEN, DT/ $\overline{\text{R}}$ ) and control inputs (CEN/ $\overline{\text{AEN}}$ , CENL, CMDLY, MB, and  $\overline{\text{READY}}$ ) are identical for all read bus cycles. Read cycles differ only in which command output is activated. The MCE control output is only asserted during interrupt acknowledge cycles.

Write bus cycles activate different control and command outputs with different timing than read bus cycles. Memory write and I/O write are write bus cycles whose timing for command outputs (MWTC and IOWC), control outputs (ALE, DEN, DT/R) and control inputs (CEN/AEN, CENL, CMDLY, MB, and READY) are identical. They differ only in which command output is activated.

Halt bus cycles are different because no command or control output is activated. All control inputs are ignored until the next bus cycle is started via  $\overline{S1}$  and  $\overline{S0}$ .

### Static Operation

All 82C288 circuitry is of static design. Internal registers and logic are static and require no refresh as with dynamic circuit design. This eliminates the minimum operating frequency restriction placed on the HMOS 82288. The CHMOS III 82C288 can operate from DC to the appropriate upper frequency limit.

The clock may be stopped in either state (HIGH/LOW) and held there indefinitely.

Power dissipation is directly related to operating frequency. As the system frequency is reduced, so is the operating power. When the clock is stopped to the 82C288, power dissipation is at a minimum. This is useful for low-power and portable applications.

### FUNCTIONAL DESCRIPTION

#### Introduction

The 82C288 bus controller is used in 80286 systems to provide address latch control, data transceiver control, and standard level-type command outputs. The command outputs are timed and have sufficient drive capabilities for large TTL buses and meet all IEEE-796 requirements for MULTIBUS I. A special MULTIBUS I mode is provided to satisfy all address/ data setup and hold time requirements. Command timing may be tailored to special needs via a CMDLY input to determine the start of a command and READY to determine the end of a command.

Connection to multiple buses are supported with a latched enable input (CENL). An address decoder can determine which, if any, bus controller should be enabled for the bus cycle. This input is latched to allow an address decoder to take full advantage of the pipelined timing on the 80286 local bus.

Buses shared by several bus controllers are supported. An AEN input prevents the bus controller from driving the shared bus command and data signals except when enabled by an external MULTIBUS I type bus arbiter.

Separate DEN and  $DT/\overline{R}$  outputs control the data transceivers for all buses. Bus contention is eliminated by disabling DEN before changing  $DT/\overline{R}$ . The DEN timing allows sufficient time for tristate bus drivers to enter 3-state OFF before enabling other drivers onto the same bus.

The term CPU refers to any 80286 processor or 80286 support component which may become an 80286 local bus master and thereby drive the 82C288 status inputs.

### **Processor Cycle Definition**

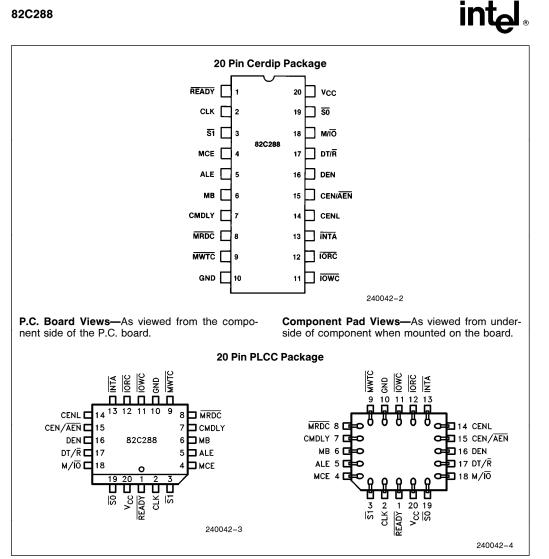

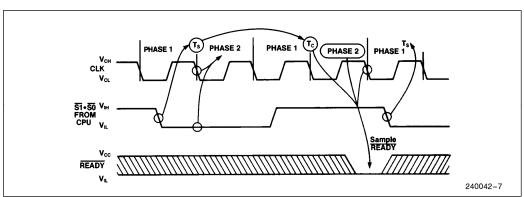

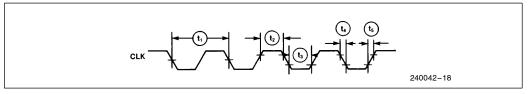

Any CPU which drives the local bus uses an internal clock which is one half the frequency of the system clock (CLK) (see Figure 3). Knowledge of the phase of the local bus master internal clock is required for proper operation of the 80286 local bus. The local bus master informs the bus controller of its internal clock phase when it asserts the status signals. Status signals are always asserted beginning in Phase 1 of the local bus master's internal clock.

Figure 3. CLK Relationship to the Processor Clock and Bus T-States

### **Bus State Definition**

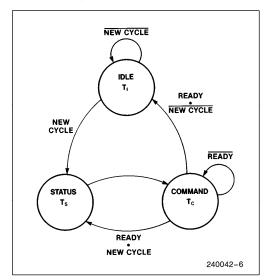

The 82C288 bus controller has three bus states (see Figure 4): Idle ( $T_I$ ) Status ( $T_S$ ) and Command ( $T_C$ ). Each bus state is two CLK cycles long. Bus state phases correspond to the internal CPU processor clock phases.

The  $T_I$  bus state occurs when no bus cycle is currently active on the 80286 local bus. This state may be repeated indefinitely. When control of the local bus is being passed between masters, the bus remains in the  $T_I$  state.

Figure 4. 82C288 Bus States

### **Bus Cycle Definition**

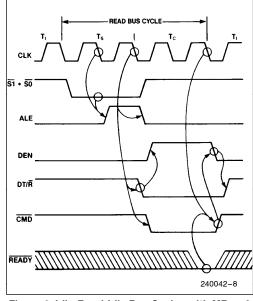

The  $\overline{S1}$  and  $\overline{S0}$  inputs signal the start of a bus cycle. When either input becomes LOW, a bus cycle is started. The T<sub>S</sub> bus state is defined to be the two CLK cycles during which either  $\overline{S1}$  or  $\overline{S0}$  are active (see Figure 5). These inputs are sampled by the 82C288 at every falling edge of CLK. When either  $\overline{S1}$  or  $\overline{S0}$  are sampled LOW, the next CLK cycle is considered the second phase of the internal CPU clock cycle.

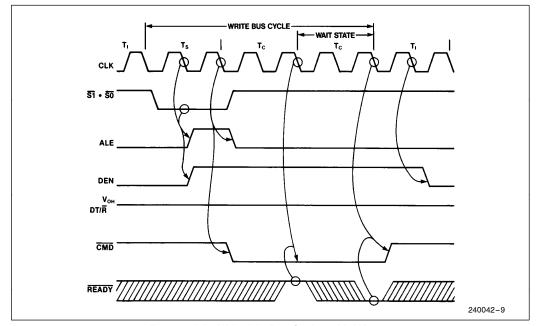

The local bus enters the  ${\sf T}_C$  bus state after the  ${\sf T}_S$  state. The shortest bus cycle may have one  ${\sf T}_S$  state and one  ${\sf T}_C$  state. Longer bus cycles are formed by repeating  ${\sf T}_C$  state. A repeated  ${\sf T}_C$  bus state is called a wait state.

The  $\overline{\text{READY}}$  input determines whether the current  $T_C$  bus state is to be repeated. The  $\overline{\text{READY}}$  input has the same timing and effect for all bus cycles.  $\overline{\text{READY}}$  is sampled at the end of each  $T_C$  bus state to see if it is active. If sampled HIGH, the  $T_C$  bus state is repeated. This is called inserting a wait state. The control and command outputs do not change during wait states.

When  $\overline{\text{READY}}$  is sampled LOW, the current bus cycle is terminated. Note that the bus controller may enter the  $T_S$  bus state directly from  $T_C$  if the status lines are sampled active at the next falling edge of CLK.

Figure 5. Bus Cycle Definition

82C288

intel

Figures 6 through 10 show the basic command and control output timing for read and write bus cycles. Halt bus cycles are not shown since they activate no outputs. The basic idle-read-idle and idle-write-idle bus cycles are shown. The signal label CMD represents the appropriate command output for the bus cycle. For Figures 6 through 10, the CMDLY input is connected to GND and CENL to  $V_{CC}$ . The effects of CENL and CMDLY are described later in the section on control inputs.

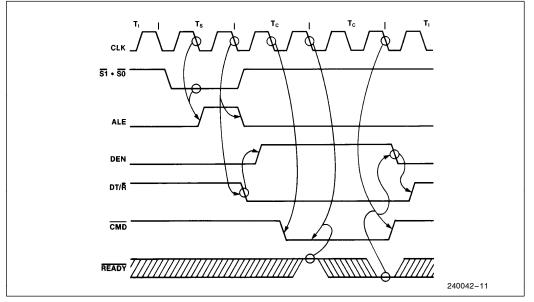

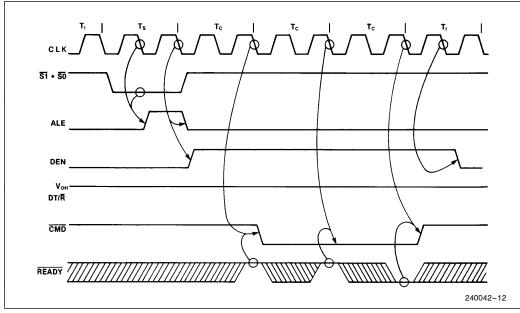

Figures 6, 7 and 8 show non-MULTIBUS I cycles. MB is connected to GND while CEN is connected to  $V_{CC}$ . Figure 6 shows a read cycle with no wait states while Figure 7 shows a write cycle with one wait state. The READY input is shown to illustrate how wait states are added.

Figure 6. Idle-Read-Idle Bus Cycles with MB = 0

Figure 7. Idle-Write-Idle Bus Cycles with MB = 0

Bus cycles can occur back to back with no T<sub>I</sub> bus states between T<sub>C</sub> and T<sub>S</sub>. Back to back cycles do not affect the timing of the command and control outputs. Command and control outputs always reach the states shown for the same clock edge (within T<sub>S</sub>, T<sub>C</sub> or following bus state) of a bus cycle.

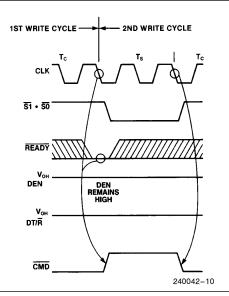

A special case in control timing occurs for back to back write cycles with MB = 0. In this case,  $DT/\overline{R}$  and DEN remain HIGH between the bus cycles (see Figure 8). The command and ALE output timing does not change.

Figures 9 and 10 show a MULTIBUS I cycle with MB = 1.  $\overline{AEN}$  and CMDLY are connected to GND. The effects of CMDLY and  $\overline{AEN}$  are described later in the section on control inputs. Figure 9 shows a read cycle with one wait state and Figure 10 shows a write cycle with two wait states. The second wait state of the write cycle is shown only for example purposes and is not required. The READY input is shown to illustrate how wait states are added.

Figure 8. Write-Write Bus Cycles with MB = 0

Figure 9. Idle-Read-Idle Bus Cycles with 1 Wait State and with MB = 1

82C288

Figure 10. Idle-Write-Idle Bus Cycles with 2 Wait States and with MB = 1

The MB control input affects the timing of the command and DEN outputs. These outputs are automatically delayed in MULTIBUS I mode to satisfy three requirements:

- 1) 50 ns minimum setup time for valid address before any command output becomes active.

- 50 ns minimum setup time for valid write data before any write command output becomes active.

- 65 ns maximum time from when any read command becomes inactive until the slave's read data drivers reach 3-state OFF.

Three signal transitions are delayed by MB = 1 as compared to MB = 0:

- 1) The HIGH to LOW transition of the read command outputs (IORC, MRDC, and INTA) are delayed one CLK cycle.

- The HIGH to LOW transition of the write command outputs (IOWC and MWTC) are delayed two CLK cycles.

- The LOW to HIGH transition of DEN for write cycles is delayed one CLK cycle.

Back to back bus cycles with MB = 1 do not change the timing of any of the command or control outputs. DEN always becomes inactive between bus cycles with MB = 1.

Except for a halt or shutdown bus cycle, ALE will be issued during the second half of  $T_S$  for any bus cycle. ALE becomes inactive at the end of the  $T_S$  to allow latching the address to keep it stable during the entire bus cycle. The address outputs may change during Phase 2 of any  $T_C$  bus state. ALE is not affected by any control input.

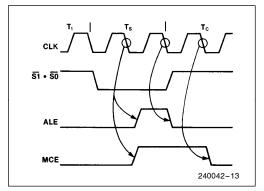

Figure 11 shows how MCE is timed during interrupt acknowledIge (INTA) bus cycles. MCE is one CLK cycle longer than ALE to hold the cascade address from a master 8259A valid after the falling edge of ALE. With the exception of the MCE control output, an INTA bus cycle is identical in timing to a read bus cycle. MCE is not affected by any control input.

# intel

Figure 11. MCE Operation for an INTA Bus Cycle

#### **Control Inputs**

The control intputs can alter the basic timing of command outputs, allow interfacing to multiple buses, and share a bus between different masters. For many 80286 systems, each CPU will have more than one bus which may be used to perform a bus cycle. Normally, a CPU will only have one bus controller active for each bus cycle. Some buses may be shared by more than one CPU (i.e. MULTIBUS) requiring only one of them use the bus at a time.

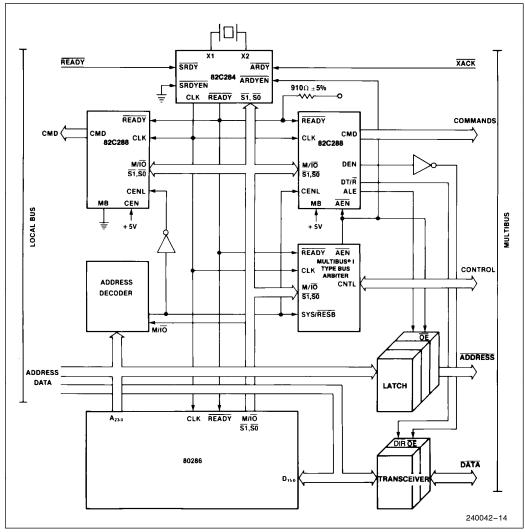

Systems with multiple and shared buses use two control input signals of the 82C288 bus controller, CENL and  $\overline{\text{AEN}}$  (see Figure 12). CENL enables the bus controller to control the current bus cycle. The  $\overline{\text{AEN}}$  input prevents a bus controller from driving its command outputs.  $\overline{\text{AEN}}$  HIGH means that another bus controller may be driving the shared bus.

In Figure 12, two buses are shown: a local bus and a MULTIBUS I. Only one bus is used for each CPU bus cycle. The CENL inputs of the bus controller select which bus controller is to perform the bus cycle. An address decoder determines which bus to use for each bus cycle. The 82C288 connected to the shared MULTIBUS I must be selected by CENL and be given access to the MULTIBUS I by AEN before it will begin a MULTIBUS I operation.

CENL must be sampled HIGH at the end of the  $T_S$  bus state (see waveforms) to enable the bus controller to activate its command and control outputs. If sampled LOW the commands and DEN will not go active and DT/ $\overline{R}$  will remain HIGH. The bus controller will ignore the CMDLY, CEN, and  $\overline{READY}$  inputs until another bus cycle is started via  $\overline{S1}$  and  $\overline{S0}$ . Since an address decoder is commonly used to identify which bus is required for each bus cycle, CENL is latched to avoid the need for latching its input.

The CENL input can affect the DEN control output. When MB = 0, DEN normally becomes active during Phase 2 of T<sub>S</sub> in write bus cycles. This transition occurs before CENL is sampled. If CENL is sampled LOW, the DEN output will be forced LOW during T<sub>C</sub> as shown in the timing waveforms.

When MB = 1, CEN/AEN becomes  $\overline{AEN}$ .  $\overline{AEN}$  controls when the bus controller command outputs enter and exit 3-state OFF.  $\overline{AEN}$  is intended to be driven by a MULTIBUS I type bus arbiter, which assures only one bus controller is driving the shared bus at any time. When  $\overline{AEN}$  makes a LOW to HIGH transition, the command outputs immediately enter 3-state OFF and DEN is forced inactive. An inactive DEN should force the local data transceivers connected to the shared data bus into 3-state OFF (see Figure 12). The LOW to HIGH transition of  $\overline{AEN}$  should only occur during T<sub>I</sub> or T<sub>S</sub> bus states.

The HIGH to LOW transition of AEN signals that the bus controller may now drive the shared bus command signals. Since a bus cycle may be active or be in the process of starting, AEN can become active during any T-state. AEN LOW immediately allows DEN to go to the appropriate state. Three CLK edges later, the command outputs will go active (see timing waveforms). The MULTIBUS I requires this delay for the address and data to be valid on the bus before the command becomes active.

When MB = 0,  $CEN/\overline{AEN}$  becomes CEN. CEN is an asynchronous input which immediately affects the command and DEN outputs. When CEN makes a HIGH to LOW transition, the commands and DEN

are immediately forced inactive. When CEN makes a LOW to HIGH transition, the commands and DEN outputs immediately go to the appropriate state (see timing waveforms). READY must still become active to terminate a bus cycle if CEN remains LOW for a selected bus controller (CENL was latched HIGH).

Some memory or I/O systems may require more address or write data setup time to command active than provided by the basic command output timing. To provide flexible command timing, the CMDLY input can delay the activation of command outputs. The CMDLY input must be sampled LOW to activate the command outputs. CMDLY does not affect the control outputs ALE, MCE, DEN, and  $DT/\overline{R}$ .

Figure 12. System Use of AEN and CENL

CMDLY is first sampled on the falling edge of the CLK ending T<sub>S</sub>. If sampled HIGH, the command output is not activated, and CMDLY is again sampled on the next falling edge of CLK. Once sampled LOW, the proper command output becomes active immediately if MB = 0. If MB = 1, the proper command goes active no earlier than shown in Figures 9 and 10.

$\overline{\text{READY}}$  can terminate a bus cycle before CMDLY allows a command to be issued. In this case no commands are issued an the bus controller will deactivate DEN and DT/ $\overline{\text{R}}$  in the same manner as if a command had been issued.

### **Waveforms Discussion**

The waveforms show the timing relationships of inputs and outputs and do not show all possible transitions of all signals in all modes. Instead, all signal timing relationships are shown via the general cases. Special cases are shown when needed. The waveforms provide some functional descriptions of the 82C288; however, most functional descriptions are provided in Figures 5 through 11.

To find the timing specification for a signal transition in a particular mode, first look for a special case in the waveforms. If no special case applies, then use a timing specification for the same or related function in another mode.

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias | $0^{\circ}C$ to $+70^{\circ}C$ |

|--------------------------------|--------------------------------|

| Storage Temperature            | -65°C to +150°C                |

| Voltage on Any Pin with        |                                |

| Respect to GND                 | -0.5V to +7V                   |

| Power Dissipation              | 1 Watt                         |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### D.C. CHARACTERISTICS $V_{CC} = 5V \pm 5\%$ , $T_{CASE} = 0^{\circ}C$ to $85^{\circ}C^*$

| Symbol           | Parameter                                                 | Min                                            | Max            | Units            | Test Conditions                                                                                                                                                                    |

|------------------|-----------------------------------------------------------|------------------------------------------------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input LOW Voltage                                         | -0.5                                           | 0.8            | V                |                                                                                                                                                                                    |

| V <sub>IH</sub>  | Input HIGH Voltage                                        | 2.0                                            | $V_{CC} + 0.5$ | V                |                                                                                                                                                                                    |

| V <sub>ILC</sub> | CLK Input LOW Voltage                                     | -0.5                                           | 0.6            | V                |                                                                                                                                                                                    |

| VIHC             | CLK Input HIGH Voltage                                    | 3.8                                            | $V_{CC} + 0.5$ | V                |                                                                                                                                                                                    |

| V <sub>OL</sub>  | Output LOW Voltage<br>Command Outputs<br>Control Outputs  |                                                | 0.45<br>0.45   | V<br>V           | I <sub>OL</sub> = 32 mA (Note 1)<br>I <sub>OL</sub> = 16 mA (Note 2)                                                                                                               |

| V <sub>OH</sub>  | Output HIGH Voltage<br>Command Outputs<br>Control Outputs | 2.4<br>$V_{CC} - 0.5$<br>2.4<br>$V_{CC} - 0.5$ |                | V<br>V<br>V<br>V | $I_{OH} = -5 \text{ mA} \text{ (Note 1)}$<br>$I_{OH} = -1 \text{ mA} \text{ (Note 1)}$<br>$I_{OH} = -1 \text{ mA} \text{ (Note 2)}$<br>$I_{OH} = -0.2 \text{ mA} \text{ (Note 2)}$ |

| ۱ <sub>۱L</sub>  | Input Leakage Current                                     |                                                | ±10            | μΑ               | $0V \leq V_{IN} \leq V_{CC}$                                                                                                                                                       |

| I <sub>LO</sub>  | Output Leakage Current                                    |                                                | ±10            | μΑ               | $0.45V \leq V_{OUT} \leq V_{CC}$                                                                                                                                                   |

| I <sub>CC</sub>  | Power Supply Current                                      |                                                | 75             | mA               |                                                                                                                                                                                    |

| I <sub>CCS</sub> | Power Supply Current (Static)                             |                                                | 3              | mA               | (Note 3)                                                                                                                                                                           |

| C <sub>CLK</sub> | CLK Input Capacitance                                     |                                                | 12             | pF               | $F_{C} = 1 \text{ MHz}$                                                                                                                                                            |

| Cl               | Input Capacitance                                         |                                                | 10             | pF               | $F_{C} = 1 \text{ MHz}$                                                                                                                                                            |

| CO               | Input/Output Capacitance                                  | T is not an                                    | 20             | pF               | $F_{C} = 1 MHz$                                                                                                                                                                    |

$T_A$  is guaranteed from 0°C to +70°C as long as  $T_{CASE}$  is not exceeded.

#### NOTES:

1. Command Outputs are INTA, IORC, IOWC, MRDC and MWRC.

2. Control Outputs are  $DT/\overline{R}$ , DEN, ALE and MCE.

3. Tested while outputs are unloaded, and inputs at  $V_{\mbox{CC}}$  or  $V_{\mbox{SS}}.$

# A.C. CHARACTERISTICS

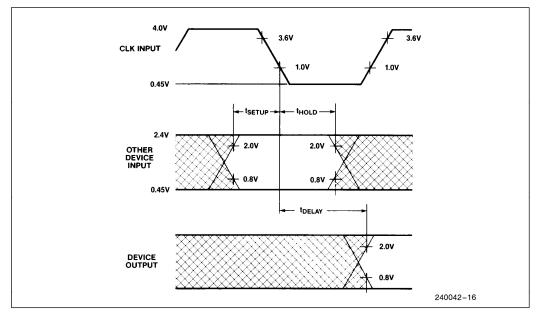

$V_{CC}=$  5V,  $\pm 5\%$ ,  $T_{CASE}=$  0°C to  $+85^{\circ}C.^{*}$  AC timings are referenced to 0.8V and 2.0V points of signals as illustrated in data sheet waveforms, unless otherwise noted.

|        |                                           | 8 1       | ЛНz       | 10         | MHz        | 12.5 MHz   |            |      | Test        |

|--------|-------------------------------------------|-----------|-----------|------------|------------|------------|------------|------|-------------|

| Symbol | Parameter                                 | -8<br>Min | -8<br>Max | -10<br>Min | -10<br>Max | -12<br>Min | -12<br>Max | Unit | Condition   |

| 1      | CLK Period                                | 62        | 250       | 50         | 250        | 40         | 250        | ns   |             |

| 2      | CLK HIGH Time                             | 20        |           | 16         |            | 13         |            | ns   | at 3.6V     |

| 3      | CLK LOW Time                              | 15        |           | 12         |            | 11         |            | ns   | at 1.0V     |

| 4      | CLK Rise Time                             |           | 10        |            | 8          |            | 8          | ns   | 1.0V to 3.6 |

| 5      | CLK Fall Time                             |           | 10        |            | 8          |            | 8          | ns   | 3.6V to 1.0 |

| 6      | M/IO and Status<br>Setup Time             | 22        |           | 18         |            | 15         |            | ns   |             |

| 7      | M/IO and Status<br>Hold Time              | 1         |           | 1          |            | 1          |            | ns   |             |

| 8      | CENL Setup Time                           | 20        |           | 15         |            | 15         |            | ns   |             |

| 9      | CENL Hold Time                            | 1         |           | 1          |            | 1          |            | ns   |             |

| 10     | READY Setup Time                          | 38        |           | 26         |            | 18         |            | ns   |             |

| 11     | READY Hold Time                           | 25        |           | 25         |            | 20         |            | ns   |             |

| 12     | CMDLY Setup Time                          | 20        |           | 15         |            | 15         |            | ns   |             |

| 13     | CMDLY Hold Time                           | 1         |           | 1          |            | 1          |            | ns   |             |

| 14     | AEN Setup Time                            | 20        |           | 15         |            | 15         |            | ns   | (Note 3)    |

| 15     | AEN Hold Time                             | 0         |           | 0          |            | 0          |            | ns   | (Note 3)    |

| 16     | ALE, MCE Active<br>Delay from CLK         | 3         | 20        | 3          | 16         | 3          | 16         | ns   | (Note 4)    |

| 17     | ALE, MCE Inactive<br>Delay from CLK       |           | 25        |            | 19         |            | 19         | ns   | (Note 4)    |

| 18     | DEN (Write)<br>Inactive from CENL         |           | 35        |            | 23         |            | 23         | ns   | (Note 4)    |

| 19     | DT/R LOW from CLK                         |           | 25        |            | 23         |            | 23         | ns   | (Note 4)    |

| 20     | DEN (Read) Active $\overline{R}$ from DT/ | 5         | 35        | 5          | 21         | 5          | 21         | ns   | (Note 4)    |

| 21     | DEN (Read) Inactive<br>Dly from CLK       | 3         | 35        | 3          | 21         | 3          | 19         | ns   | (Note 4)    |

| 22     | $DT/\overline{R}$ HIGH from DEN Inactive  | 5         | 35        | 5          | 20         | 5          | 18         | ns   | (Note 4)    |

| 23     | DEN (Write) Active<br>Delay from CLK      |           | 30        |            | 23         |            | 23         | ns   | (Note 4)    |

| 24     | DEN (Write) Inactive<br>Dly from CLK      | 3         | 30        | 3          | 19         | 3          | 19         | ns   | (Note 4)    |

$^*T_{\mbox{A}}$  is guaranteed from 0°C to  $\,+\,70^{\circ}\mbox{C}$  as long as  $T_{\mbox{CASE}}$  is not exceeded.

## A.C. CHARACTERISTICS

$V_{CC}=$  5V,  $\pm 5\%$ ,  $T_{CASE}=$  0°C to  $+85^{\circ}C.^{*}$  AC timings are referenced to 0.8V and 2.0V points of signals as illustrated in data sheet waveforms, unless otherwise noted. (Continued)

|        |                                                     | 8 M       | lHz       | 10 MHz     |            | 12.5 MHz   |            |      | Test      |

|--------|-----------------------------------------------------|-----------|-----------|------------|------------|------------|------------|------|-----------|

| Symbol | Parameter                                           | -8<br>Min | -8<br>Max | -10<br>Min | -10<br>Max | -12<br>Min | -12<br>Max | Unit | Condition |

| 25     | DEN Inactive from<br>CEN                            |           | 30        |            | 25         |            | 25         | ns   | (Note 4)  |

| 26     | DEN Active from<br>CEN                              |           | 30        |            | 24         |            | 24         | ns   | (Note 4)  |

| 27     | $DT/\overline{R}$ HIGH from CLK<br>(when CEN = LOW) |           | 35        |            | 25         |            | 25         | ns   | (Note 4)  |

| 28     | DEN Active from AEN                                 |           | 30        |            | 26         |            | 26         | ns   | (Note 4)  |

| 29     | CMD Active Delay<br>from CLK                        | 3         | 25        | 3          | 21         | 3          | 21         | ns   | (Note 5)  |

| 30     | CMD Inactive Delay<br>from CLK                      | 5         | 20        | 5          | 20         | 5          | 20         | ns   | (Note 5)  |

| 31     | CMD Active from<br>CEN                              |           | 25        |            | 25         |            | 25         | ns   | (Note 5)  |

| 32     | CMD Inactive from CEN                               |           | 25        |            | 25         |            | 25         | ns   | (Note 5)  |

| 33     | CMD Inactive Enable from AEN                        |           | 40        |            | 40         |            | 40         | ns   | (Note 5)  |

| 34     | CMD Float Delay from AEN                            |           | 40        |            | 40         |            | 40         | ns   | (Note 6)  |

| 35     | MB Setup Time                                       | 20        |           | 20         |            | 20         |            | ns   |           |

| 36     | MB Hold Time                                        | 0         |           | 0          |            | 0          |            | ns   |           |

| 37     | Command Inactive Enable from MB $\downarrow$        |           | 40        |            | 40         |            | 40         | ns   | (Note 5)  |

| 38     | Command Float Time from MB 1                        |           | 40        |            | 40         |            | 40         | ns   | (Note 6)  |

| 39     | DEN Inactive from MB 1                              |           | 30        |            | 26         |            | 26         | ns   | (Note 4)  |

| 40     | DEN Active from MB $\downarrow$                     |           | 30        |            | 30         |            | 30         | ns   | (Note 4)  |

$^*T_A$  is guaranteed from 0°C to  $\,+\,70^\circ C$  as long as  $T_{CASE}$  is not exceeded.

#### NOTES:

ACT is:

AEN is an asynchronous input. This specification is for testing purposes only, to assure recognition at a specific CLK edge.

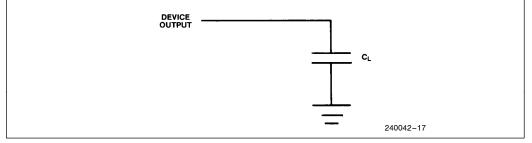

Control output load: Cl = 150 pF.

Command output load: Cl = 300 pF.

Float condition occurs when output current is less than I<sub>LO</sub> in magnitude.

Note 7: AC Setup, Hold and Delay Time Measurement—General

Note 8: AC Test Loading on Outputs

### WAVEFORMS

### **CLK CHARACTERISTICS**

### WAVEFORMS (Continued)

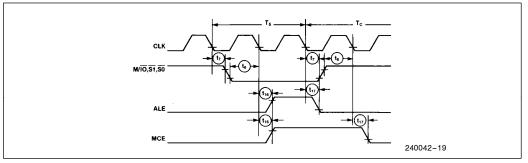

### STATUS, ALE, MCE, CHARACTERISTICS

### CENL, CMDLY, DEN CHARACTERISTICS WITH MB = 0 AND CEN = 1 DURING WRITE CYCLE

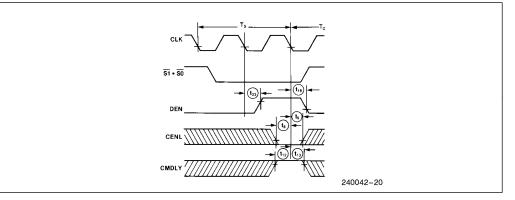

### READ CYCLE CHARACTERISTICS WITH MB = 0 AND CEN = 1

18

# WAVEFORMS (Continued)

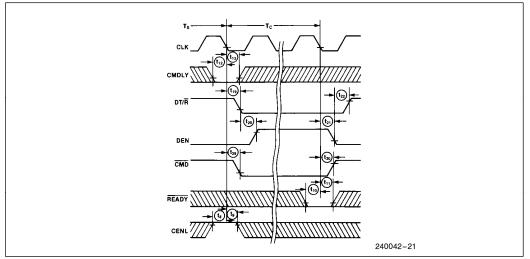

# WRITE CYCLE CHARACTERISTIC WITH MB = 0 AND CEN = 1

CEN CHARACTERISTICS WITH MB = 0

### WAVEFORMS (Continued)

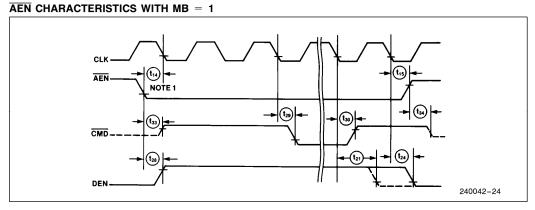

**NOTE:** 1. AEN is an asynchronous input. AEN setup and hold time is specified to guarantee the response shown in the waveforms.

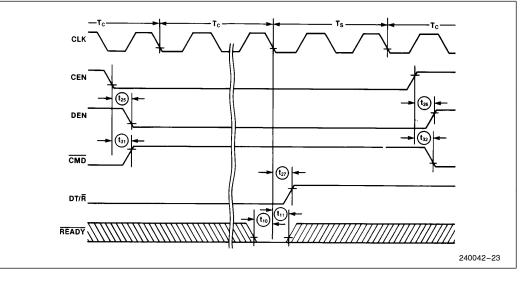

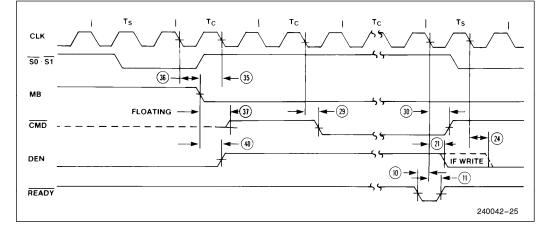

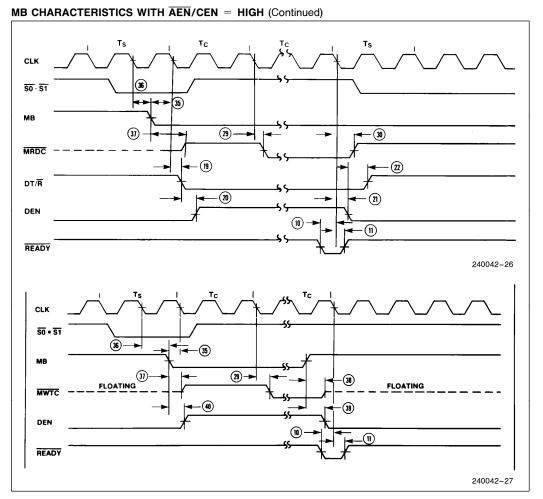

### MB CHARACTERISTICS WITH $\overline{\text{AEN}}/\text{CEN} = \text{HIGH}$

### WAVEFORMS (Continued)

#### NOTES:

MB is an asynchronous input. MB setup and hold times specified to guarantee the response shown in the waveforms.

If the setup time, t35, is met two clock cycles will occur before CMD becomes active after the falling edge of MB.

## DATA SHEET REVISION REVIEW

The following list represents key differences between this and the -002 data sheet. Please review this summary carefully.

- 1. The  $I_{\mbox{\scriptsize CCS}}$  specification was changed from 1 mA to 3 mA maximum.

- 2. The "PRELIMINARY" markings have been removed from the data sheet.