Chip Size: Chip Size Tolerance: Chip Thickness:  $2.74 \times 1.31$  mm (108  $\times$  51.6 mils) ±10 µm (±0.4 mils) 127 ± 15 µm (5.0 ± 0.6 mils)

### Features

- 26 dBm Output P<sub>(-1dB)</sub> at 28 GHz

- High Gain: 18 dB

- $50\Omega$  Input/Output Matching

- Small Size

- RF Detector Network

# Description

The HMMC-5033 is a MMIC power amplifier designed for use in wireless transmitters that operate within the 17.7 GHz to 32 GHz range. At 28 GHz it provides 26 dBm of output power (P-1dB) and 18 dB of small-signal gain from a small easy-to-use device. The HMMC-5033 was designed to be driven by the HMMC-5040 (20-40 GHz) or the HMMC-5618 (5.9-20 GHz) MMIC amplifier for linear transmit applications. This device has input and output matching circuitry for use in 50 ohm environments.

# Absolute Maximum Ratings<sup>[1]</sup>

| Symbol                           | Parameters/Conditions              | Min. | Max. | Units |

|----------------------------------|------------------------------------|------|------|-------|

| V <sub>D1,2</sub>                | Drain Supply Voltages              |      | 5.2  | Volts |

| V <sub>G1</sub> ,V <sub>GG</sub> | Gate Supply Voltages               | -3.0 | 0.5  | Volts |

| I <sub>D1</sub>                  | First Stage Drain Current          |      | 320  | mA    |

| I <sub>D2</sub>                  | Second Stage Drain Current         |      | 640  | mA    |

| P <sub>in</sub>                  | RF Input Power                     |      | 23   | dBm   |

| Det.Bias                         | Applied Detector Bias (Optional)   |      | 5.2  | Volts |

| T <sub>ch</sub>                  | Channel Temperature <sup>[2]</sup> |      | 170  | °C    |

| Τ <sub>Α</sub>                   | Backside Ambient Temperature       | -55  | +85  | °C    |

| T <sub>st</sub>                  | Storage Temperature                | -65  | +170 | °C    |

| T <sub>max</sub>                 | Maximum Assembly Temperature       |      | 300  | °C    |

<sup>[1]</sup>Absolute maximum ratings for continuous operation unless otherwise noted. <sup>[2]</sup>Refer to *DC Specifications / Physical Properties* table for derating information.

| Symbol                           | Parameters/Conditions                                                                                                                | Min. | Тур.     | Max. | Units   |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|---------|

| V <sub>D1</sub>                  | Drain Supply Operating Voltage                                                                                                       |      | 3.5      | 5    | Volts   |

| V <sub>D2</sub>                  | Drain Supply Operating Voltage                                                                                                       |      | 5        | 5    | Volts   |

| I <sub>D1</sub>                  | First Stage Drain Supply Current ( $V_{D1} = 3.5 V$ , $V_{G1} = Open$ , $V_{GG}$ set for $I_{D2}$ typical)                           |      | 240      | 320  | mA      |

| I <sub>D2</sub>                  | Second Stage Drain Supply Current $(V_{D2} = 5 \text{ V}, V_{GG} \cong -0.8 \text{ V})$                                              |      | 460      | 640  | mA      |

| V <sub>G1</sub> ,V <sub>GG</sub> | Gate Supply Operating Voltages ( $I_{D1} + I_{D2} \cong 700 \text{ mA}$ )                                                            |      | -0.8     |      | Volts   |

| V <sub>P</sub>                   | Pinch-off Voltage [ $V_{DD}$ = 2.5 V, ( $I_{D1}$ + $I_{D2}$ ) $\leq$ 20 mA]                                                          | -2.5 | -1.2     | -0.8 | Volts   |

| Det.Bias                         | Detector Bias Voltage (Optional)                                                                                                     |      | $V_{D2}$ | 5    | Volts   |

| θ <sub>1(ch-bs)</sub>            | First Stage Thermal Resistance <sup>[2]</sup><br>(Channel-to-Backside at T <sub>ch</sub> = 160°C)                                    |      | 67       |      | °C/Watt |

| θ <sub>2(ch-bs)</sub>            | Second Stage Thermal Resistance[2]<br>(Channel-to-Backside at T <sub>ch</sub> = 160°C)                                               |      | 37       |      | °C/Watt |

| T <sub>ch</sub>                  | Second Stage Channel Temperature <sup>[3]</sup><br>( $T_A = 75^{\circ}C$ , MTTF $\ge 10^{6}$ hrs, $V_{D2} = 5$ V, $I_{D2} = 460$ mA) |      | 160      |      | °C      |

# DC Specifications/Physical Properties<sup>[1]</sup>

<sup>[1]</sup>Backside ambient operating temperature  $T_A = 25^{\circ}C$  unless otherwise noted. <sup>[2]</sup>Thermal resistance (°C/Watt) at a channel temperature T(°C) can be *estimated* using the equation:  $\theta(T) \cong \theta_{ch-bs} \times [T(^{\circ}C)+273] / [160^{\circ}C+273].$ <sup>[3]</sup>Derate MTTF by a factor of two for every 8°C above T<sub>ch</sub>.

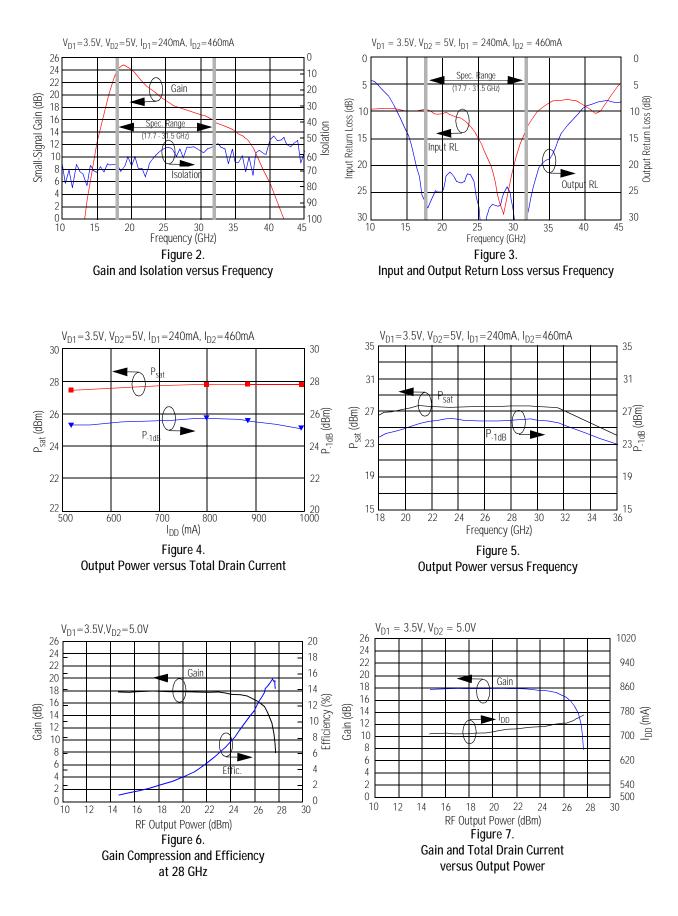

# **RF** Specifications

$(T_A = 25^{\circ}C, Z_0 = 50 \Omega, V_{D1} = 3.5 V, V_{D2} = 5 V, I_{D2} = 460 \text{ mA} [I_{D1} \cong 240 \text{ mA}])$

| Symbol                              | Parameters/Conditions                   |      |     |     |     | oppoi |      |     |     |      |     | Units |

|-------------------------------------|-----------------------------------------|------|-----|-----|-----|-------|------|-----|-----|------|-----|-------|

|                                     |                                         | Min  | Тур | Max | Min | Тур   | Max  | Min | Тур | Max  |     |       |

| BW                                  | Operating Bandwidth                     | 17.7 |     | 21  | 21  |       | 26.5 | 25  |     | 31.5 | GHz |       |

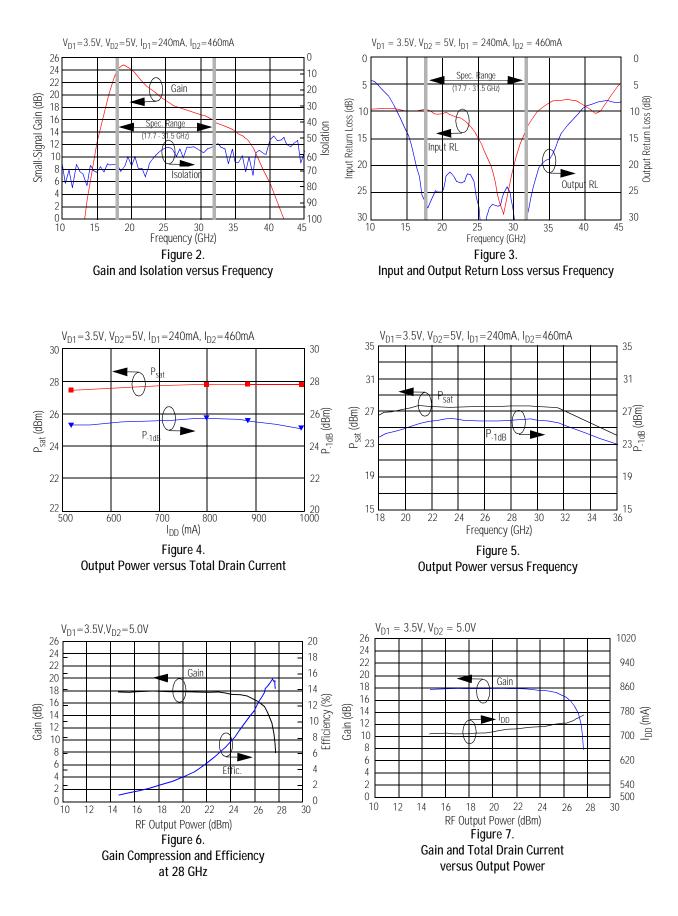

| Gain                                | Small Signal Gain                       | 17   | 22  |     | 17  | 20    |      | 15  | 18  |      | dB  |       |

| P <sub>-1dB</sub>                   | Output Power<br>at 1dB Gain Compression | 22   | 23  |     | 24  | 25    |      | 25  | 26  |      | dBm |       |

| P <sub>SAT</sub>                    | Saturated Output Power <sup>[1]</sup>   |      | 25  |     |     | 27    |      |     | 28  |      | dBm |       |

| (RL <sub>in</sub> ) <sub>MIN</sub>  | Min. Input Return Loss                  | 8    | 10  |     | 9   | 12    |      | 10  | 12  |      | dB  |       |

| (RL <sub>out</sub> ) <sub>MIN</sub> | Min. Output Return Loss                 | 15   | 20  |     | 15  | 20    |      | 15  | 20  |      | dB  |       |

| Isolation                           | Min. Reverse Isolation                  |      | 50  |     |     | 50    |      |     | 50  |      | dB  |       |

<sup>[1]</sup>Note: Devices operating continuously beyond 1 dB gain compression may experience power degradation.

#### Applications

The HMMC-5033 MMIC is a broadband power amplifier designed for use in transmitters that operate in various frequency bands between 17.7 GHz and 32 GHz. It can be attached to the output of the HMMC-5040 (20-40 GHz) or the HMMC-5618 (5.9-20 GHz) MMIC amplifier, increasing the power handling capability of transmitters requiring linear operation.

#### **Biasing and Operation**

The recommended DC bias condition for optimum efficiency, performance, and reliability is  $V_{D1} = 3.5$  volts and  $V_{D2} = 5$  volts with  $V_{GG}$  set for  $I_{D1} + I_{D2} = 700$ mA (no connection to  $V_{G1}$ ). This bias arrangement results in default drain currents  $I_{D1} = 240$  mA and  $I_{D2} = 460$  mA.

A single DC gate supply connected to  $V_{GG}$  will bias all gain stages.

If operation with both  $V_{D1}$  and  $V_{D2}$  at 5 volts is desired, an additional wire bond connection from the  $V_{G1}$  pad to the  $V_{GG}$  external bypass chip-capacitor (shorting  $V_{G1}$  to  $V_{GG}$ ) will balance the currents in each gain stage.  $V_{GG}$  (=  $V_{G1}$ ) can be adjusted for  $I_{D1} + I_{D2}$  = 700 mA.

Muting can be accomplished by setting  $V_{G1}$  and/or  $V_{GG}$  to the pinchoff voltage  $V_{P.}$

An on chip RF output power detector network is provided. The differential voltage between the *Det-Ref* and *Det-Out* pads can be correlated with the RF power emerging from the *RF Output* port. Bias the diodes at ~200 mA.

The RF ports are AC-coupled at the RF input to the first stage and the RF output of the second stage.

If the output detector is biased using the on-chip optional *Det-Bias* network, an external ACblocking capacitor may be required at the *RF Output* port.

No ground wires are needed since ground connections are made with plated through-holes to the backside of the device.

#### Assembly Techniques

It is recommended that the electrical connections to the bonding pads be made using 0.7-1.0 mil diameter gold wire. The microwave/millimeter-wave connections should be kept as short as possible to minimize inductance. For assemblies requiring long bond wires, multiple wires can be attached to the RF bonding pads.

GaAs MMICs are ESD sensitive. ESD preventive measures must be employed in all aspects of storage, handling, and assembly. MMIC ESD precautions, handling considerations, die attach and bonding methods are critical factors in successful GaAs MMIC performance and reliability.

Agilent application note #54, "GaAs MMIC ESD, Die Attach and Bonding Guidelines" provides basic information on these subjects.

#### Additional References:

AN# 52, "1 Watt 17.7 GHz - 32 GHz Linear Power Amplifier," and PN# 6, "HMMC-5033 Intermodulation Distortion."

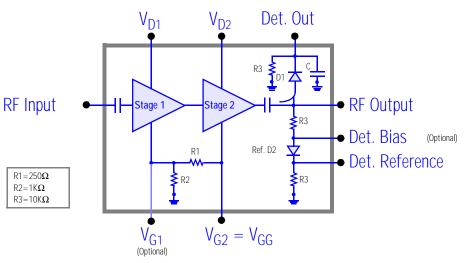

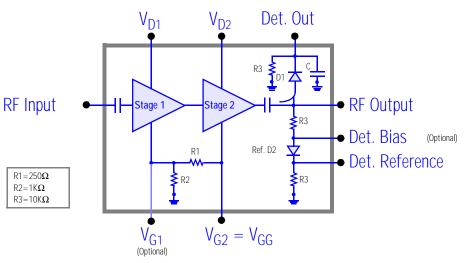

Figure 1. HMMC-5033 Simplified Schematic Diagram

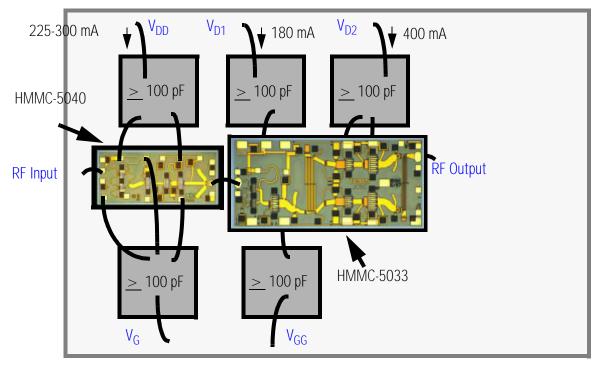

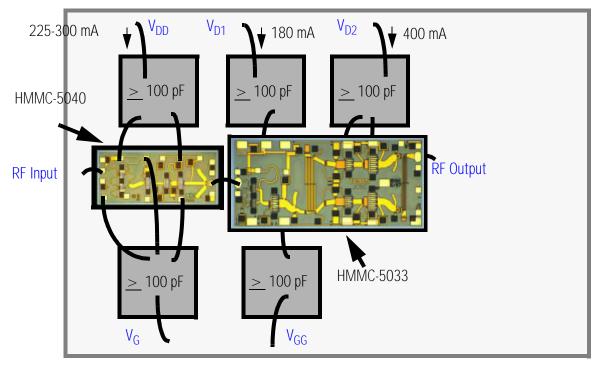

Figure 9. Assembly diagram illustrating the HMMC-5033cascaded with the HMMC-5040for 20-32 GHz applications.

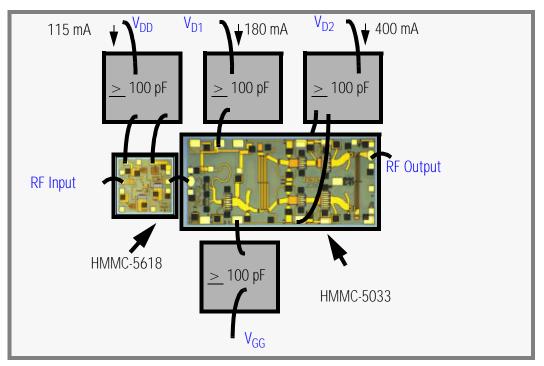

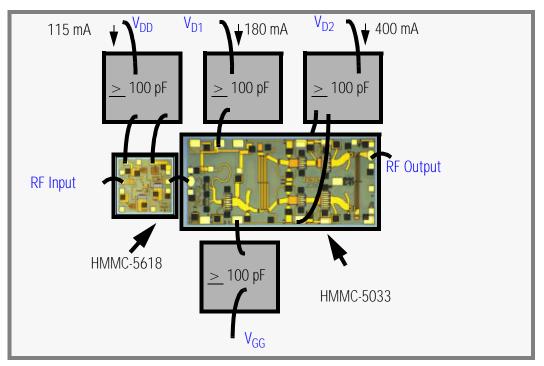

Figure 10. Assembly diagram illustrating the HMMC-5033 cascaded with the HMMC-5618 for 17.7-20 GHz applications.

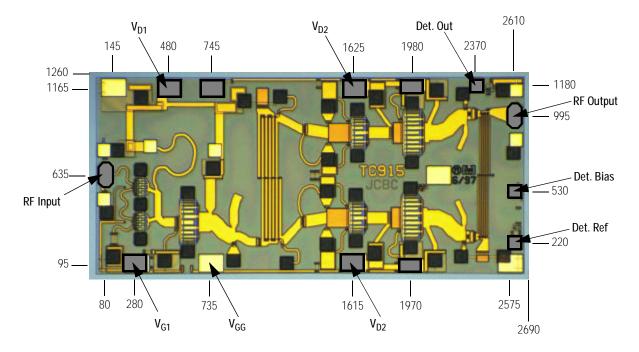

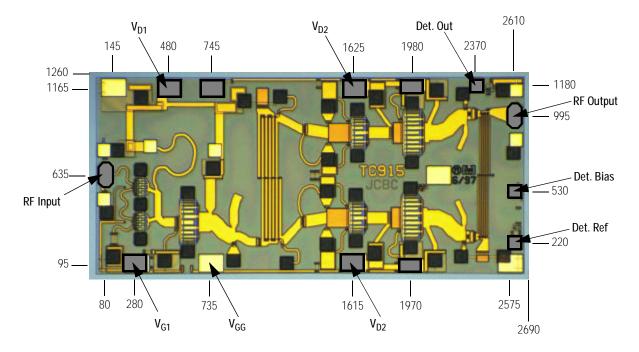

Figure 11. Bonding Pad Locations

This data sheet contains a variety of typical and guaranteed performance data. The information supplied should not be interpreted as a complete list of circuit specifications. In this data sheet the term *typical* refers to the 50th percentile performance. For additional information contact your local Agilent Technologies sales representative.

Chip Size: Chip Size Tolerance: Chip Thickness:  $2.74 \times 1.31$  mm (108  $\times$  51.6 mils) ±10 µm (±0.4 mils) 127 ± 15 µm (5.0 ± 0.6 mils)

### Features

- 26 dBm Output P<sub>(-1dB)</sub> at 28 GHz

- High Gain: 18 dB

- $50\Omega$  Input/Output Matching

- Small Size

- RF Detector Network

# Description

The HMMC-5033 is a MMIC power amplifier designed for use in wireless transmitters that operate within the 17.7 GHz to 32 GHz range. At 28 GHz it provides 26 dBm of output power (P-1dB) and 18 dB of small-signal gain from a small easy-to-use device. The HMMC-5033 was designed to be driven by the HMMC-5040 (20-40 GHz) or the HMMC-5618 (5.9-20 GHz) MMIC amplifier for linear transmit applications. This device has input and output matching circuitry for use in 50 ohm environments.

# Absolute Maximum Ratings<sup>[1]</sup>

| Symbol                           | Parameters/Conditions              | Min. | Max. | Units |

|----------------------------------|------------------------------------|------|------|-------|

| V <sub>D1,2</sub>                | Drain Supply Voltages              |      | 5.2  | Volts |

| V <sub>G1</sub> ,V <sub>GG</sub> | Gate Supply Voltages               | -3.0 | 0.5  | Volts |

| I <sub>D1</sub>                  | First Stage Drain Current          |      | 320  | mA    |

| I <sub>D2</sub>                  | Second Stage Drain Current         |      | 640  | mA    |

| P <sub>in</sub>                  | RF Input Power                     |      | 23   | dBm   |

| Det.Bias                         | Applied Detector Bias (Optional)   |      | 5.2  | Volts |

| T <sub>ch</sub>                  | Channel Temperature <sup>[2]</sup> |      | 170  | °C    |

| Τ <sub>Α</sub>                   | Backside Ambient Temperature       | -55  | +85  | °C    |

| T <sub>st</sub>                  | Storage Temperature                | -65  | +170 | °C    |

| T <sub>max</sub>                 | Maximum Assembly Temperature       |      | 300  | °C    |

<sup>[1]</sup>Absolute maximum ratings for continuous operation unless otherwise noted. <sup>[2]</sup>Refer to *DC Specifications / Physical Properties* table for derating information.

| Symbol                           | Parameters/Conditions                                                                                                                | Min. | Тур.     | Max. | Units   |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|---------|

| V <sub>D1</sub>                  | Drain Supply Operating Voltage                                                                                                       |      | 3.5      | 5    | Volts   |

| V <sub>D2</sub>                  | Drain Supply Operating Voltage                                                                                                       |      | 5        | 5    | Volts   |

| I <sub>D1</sub>                  | First Stage Drain Supply Current ( $V_{D1} = 3.5 V$ , $V_{G1} = Open$ , $V_{GG}$ set for $I_{D2}$ typical)                           |      | 240      | 320  | mA      |

| I <sub>D2</sub>                  | Second Stage Drain Supply Current $(V_{D2} = 5 \text{ V}, V_{GG} \cong -0.8 \text{ V})$                                              |      | 460      | 640  | mA      |

| V <sub>G1</sub> ,V <sub>GG</sub> | Gate Supply Operating Voltages ( $I_{D1} + I_{D2} \cong 700 \text{ mA}$ )                                                            |      | -0.8     |      | Volts   |

| V <sub>P</sub>                   | Pinch-off Voltage [ $V_{DD}$ = 2.5 V, ( $I_{D1}$ + $I_{D2}$ ) $\leq$ 20 mA]                                                          | -2.5 | -1.2     | -0.8 | Volts   |

| Det.Bias                         | Detector Bias Voltage (Optional)                                                                                                     |      | $V_{D2}$ | 5    | Volts   |

| θ <sub>1(ch-bs)</sub>            | First Stage Thermal Resistance <sup>[2]</sup><br>(Channel-to-Backside at T <sub>ch</sub> = 160°C)                                    |      | 67       |      | °C/Watt |

| θ <sub>2(ch-bs)</sub>            | Second Stage Thermal Resistance[2]<br>(Channel-to-Backside at T <sub>ch</sub> = 160°C)                                               |      | 37       |      | °C/Watt |

| T <sub>ch</sub>                  | Second Stage Channel Temperature <sup>[3]</sup><br>( $T_A = 75^{\circ}C$ , MTTF $\ge 10^{6}$ hrs, $V_{D2} = 5$ V, $I_{D2} = 460$ mA) |      | 160      |      | °C      |

# DC Specifications/Physical Properties<sup>[1]</sup>

<sup>[1]</sup>Backside ambient operating temperature  $T_A = 25^{\circ}C$  unless otherwise noted. <sup>[2]</sup>Thermal resistance (°C/Watt) at a channel temperature T(°C) can be *estimated* using the equation:  $\theta(T) \cong \theta_{ch-bs} \times [T(^{\circ}C)+273] / [160^{\circ}C+273].$ <sup>[3]</sup>Derate MTTF by a factor of two for every 8°C above T<sub>ch</sub>.

# **RF** Specifications

$(T_A = 25^{\circ}C, Z_0 = 50 \Omega, V_{D1} = 3.5 V, V_{D2} = 5 V, I_{D2} = 460 \text{ mA} [I_{D1} \cong 240 \text{ mA}])$

| Symbol                              | Parameters/Conditions                   |      |     |     |     | oppoi |      |     |     |      |     | Units |

|-------------------------------------|-----------------------------------------|------|-----|-----|-----|-------|------|-----|-----|------|-----|-------|

|                                     |                                         | Min  | Тур | Max | Min | Тур   | Max  | Min | Тур | Max  |     |       |

| BW                                  | Operating Bandwidth                     | 17.7 |     | 21  | 21  |       | 26.5 | 25  |     | 31.5 | GHz |       |

| Gain                                | Small Signal Gain                       | 17   | 22  |     | 17  | 20    |      | 15  | 18  |      | dB  |       |

| P <sub>-1dB</sub>                   | Output Power<br>at 1dB Gain Compression | 22   | 23  |     | 24  | 25    |      | 25  | 26  |      | dBm |       |

| P <sub>SAT</sub>                    | Saturated Output Power <sup>[1]</sup>   |      | 25  |     |     | 27    |      |     | 28  |      | dBm |       |

| (RL <sub>in</sub> ) <sub>MIN</sub>  | Min. Input Return Loss                  | 8    | 10  |     | 9   | 12    |      | 10  | 12  |      | dB  |       |

| (RL <sub>out</sub> ) <sub>MIN</sub> | Min. Output Return Loss                 | 15   | 20  |     | 15  | 20    |      | 15  | 20  |      | dB  |       |

| Isolation                           | Min. Reverse Isolation                  |      | 50  |     |     | 50    |      |     | 50  |      | dB  |       |

<sup>[1]</sup>Note: Devices operating continuously beyond 1 dB gain compression may experience power degradation.

#### Applications

The HMMC-5033 MMIC is a broadband power amplifier designed for use in transmitters that operate in various frequency bands between 17.7 GHz and 32 GHz. It can be attached to the output of the HMMC-5040 (20-40 GHz) or the HMMC-5618 (5.9-20 GHz) MMIC amplifier, increasing the power handling capability of transmitters requiring linear operation.

#### **Biasing and Operation**

The recommended DC bias condition for optimum efficiency, performance, and reliability is  $V_{D1} = 3.5$  volts and  $V_{D2} = 5$  volts with  $V_{GG}$  set for  $I_{D1} + I_{D2} = 700$ mA (no connection to  $V_{G1}$ ). This bias arrangement results in default drain currents  $I_{D1} = 240$  mA and  $I_{D2} = 460$  mA.

A single DC gate supply connected to  $V_{GG}$  will bias all gain stages.

If operation with both  $V_{D1}$  and  $V_{D2}$  at 5 volts is desired, an additional wire bond connection from the  $V_{G1}$  pad to the  $V_{GG}$  external bypass chip-capacitor (shorting  $V_{G1}$  to  $V_{GG}$ ) will balance the currents in each gain stage.  $V_{GG}$  (=  $V_{G1}$ ) can be adjusted for  $I_{D1} + I_{D2}$  = 700 mA.

Muting can be accomplished by setting  $V_{G1}$  and/or  $V_{GG}$  to the pinchoff voltage  $V_{P.}$

An on chip RF output power detector network is provided. The differential voltage between the *Det-Ref* and *Det-Out* pads can be correlated with the RF power emerging from the *RF Output* port. Bias the diodes at ~200 mA.

The RF ports are AC-coupled at the RF input to the first stage and the RF output of the second stage.

If the output detector is biased using the on-chip optional *Det-Bias* network, an external ACblocking capacitor may be required at the *RF Output* port.

No ground wires are needed since ground connections are made with plated through-holes to the backside of the device.

#### Assembly Techniques

It is recommended that the electrical connections to the bonding pads be made using 0.7-1.0 mil diameter gold wire. The microwave/millimeter-wave connections should be kept as short as possible to minimize inductance. For assemblies requiring long bond wires, multiple wires can be attached to the RF bonding pads.

GaAs MMICs are ESD sensitive. ESD preventive measures must be employed in all aspects of storage, handling, and assembly. MMIC ESD precautions, handling considerations, die attach and bonding methods are critical factors in successful GaAs MMIC performance and reliability.

Agilent application note #54, "GaAs MMIC ESD, Die Attach and Bonding Guidelines" provides basic information on these subjects.

#### Additional References:

AN# 52, "1 Watt 17.7 GHz - 32 GHz Linear Power Amplifier," and PN# 6, "HMMC-5033 Intermodulation Distortion."

Figure 1. HMMC-5033 Simplified Schematic Diagram

Figure 9. Assembly diagram illustrating the HMMC-5033cascaded with the HMMC-5040for 20-32 GHz applications.

Figure 10. Assembly diagram illustrating the HMMC-5033 cascaded with the HMMC-5618 for 17.7-20 GHz applications.

Figure 11. Bonding Pad Locations

This data sheet contains a variety of typical and guaranteed performance data. The information supplied should not be interpreted as a complete list of circuit specifications. In this data sheet the term *typical* refers to the 50th percentile performance. For additional information contact your local Agilent Technologies sales representative.