AN-957

# Interfacing the NM24C16 Serial EEPROM to the 8031 Microcontroller

### INTRODUCTION

This applications note describes an interface between the Fairchild Semiconductor NM24C16 serial EEPROM and an 8031 microcontroller. The interface between the devices uses 2 of the 8031 general purpose I/O port lines. Software has been developed that demonstrates how the NM24C16 can be accessed through the I/O port bits. The circuit and software has been bench tested and is ready to be used in an end user application.

#### NM24C16 DESCRIPTION

The NM24C16 is a 16k serial EEPROM that has a 2k by 8-bit architecture. The NM24C16 uses the industry standard  $I^2C$  serial protocol for data transfers.

The I<sup>2</sup>C protocol allows several devices to share the same two wire clock and data bus. Devices that are compatible with the protocol fall into the categories of being either a master or a slave. A master device controls the transfer of data, and a slave device responds to the commands issued by a master. The NM24CXX family of devices always fall into the category of slave devices since they can not initiate data transfers.

The I<sup>2</sup>C protocol uses a clock (SCL) and a bidirectional data line (SDA). When the NM24C16 is transmitting data an open drain transistor is used to control the state of the SDA line. The SDA I/ O pulls the line low for a zero state, or places the line in high impedance for a one state. An external pull-up resistor ensures a "high" condition exists when the SDA line is in a high impedance state.

Data is transfered back and forth by using predefined bit sequences. All transfers are initiated with a START condition (SDA going low with SCL high) and terminated with a STOP condition (SDA going high with SCL high). If an unexpected STOP is ever detected the NM24C16 will return to the standby mode. Because transitions of SDA when SCL is high have been defined as STOP and START conditions, the SDA line must change only when SCL is low while transfers are being performed.

#### DATA TRANSFERS

There are just two types of data transfers used on the NM24C16, a page write operation, and a sequential read operation. Byte write and byte read operations are simply truncated versions of a page write or sequential read.

The page write allows up to 16 bytes in a single page to be altered during a single write operation. It is important to note that all addresses to be altered must reside in the same 16 byte page. A byte write is the same as a page write with the data in a single address being altered.

The sequential read operation will allow read operations starting at a user defined address and then allow successive addresses to be read as long as the user continues to indicate that the read operation is to continue. The byte read is simply a sequential read from only a single address. Fairchild Application Note 957

#### **8031 INTERFACE DESCRIPTION**

The interface to the 8031 uses 2 general purpose port lines. One of the lines is used to drive the SCL input of the NM24C16, and the other is used as an I/O port connected to the SDA line. The 8031 has very weak pull-ups on the output ports that provide a high state. When an 8031 port bit is sending a high, the bit can be driven externally and used as an input.

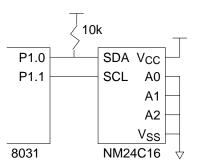

Port 1 of the 8031 provides the 2 I/O bits for the interface. Figure 1shows how the NM24C16 is connected to the 8031. The port bits that were chosen for this interface are not especially significant. Any 2 available port bits could be used as long as 1 can be configured an output and 1 as an I/O with the weak pull-up. Changes in the interface software to implement different port placements would only require a change in the SDA and SCL port definition at the top of the program.

#### FIGURE 1. NM24C16 to 8031 Connections

#### SOFTWARE DESCRIPTION

The software listing demonstrates a byte read and byte write operation. The read and write operations are implemented in separate subroutines. Parameters to be passed into the subroutines are stored in the SRAM portion of the 8031. The passed parameters include address (hi-order and low-order) and data (single byte) information. The variables are sometimes modified during subroutine operation so they must be initialized immediately prior to a subroutine call. Expansions of the byte read and write routines to implement sequential read and page write should be straightforward.

The software also implements acknowledge (ACK) polling to indicate when a write operation has completed. While the NM24C16 is actually changing the state of the EEPROM bits all input pins are ignored. Once a write cycle has concluded the NM24C16 will return an acknowledge when a valid slave address is issued. The ACK polling routine repeatedly sends a slave address and check to see if the X24C16 returns an acknowledge. A STOP condition is issued once an ACK is received to return the NM24C16 to the standby mode. Using acknowledge polling can significantly reduce the effective Write Cycle Time because the actual time required is typically much less than the maximum specified in the data sheet.

#### CONCLUSION

This applications note has shown how the NM24C16 can easily be interfaced to the 8031 microcontroller. Interface resources are minimal with only 2 I/O port pins and 200 bytes of code required.

Although this applications note describes an interface to the 8031, the issues discussed can be used to implement an 8031 interface to any general purpose microcontroller.

| ****                                                                                                                                           | ****                                                                                                      | ***             | *****                                              |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------|--|--|--|

| **************************************                                                                                                         |                                                                                                           |                 |                                                    |  |  |  |

| ;*can be interfaced to the 8031 microcontroller. The software includes *                                                                       |                                                                                                           |                 |                                                    |  |  |  |

| ;*byte read and a byte write routines.                                                                                                         |                                                                                                           |                 |                                                    |  |  |  |

| *                                                                                                                                              |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 | by using 2 general purpose I/O *                   |  |  |  |

| ;*port lines. Port 1 is used with one line driving the Nm24C16 SCL *<br>;*input and a second port line used in a bidirectional mode for SDA. * |                                                                                                           |                 |                                                    |  |  |  |

| * *                                                                                                                                            |                                                                                                           |                 |                                                    |  |  |  |

| ;*The mainli                                                                                                                                   | * * The mainline was used to test the functionality of the subroutines. *                                 |                 |                                                    |  |  |  |

| ;*The subroutines can be copied directly into a customer's program and $*$                                                                     |                                                                                                           |                 |                                                    |  |  |  |

| ;*be expected to operated as described. The final mainline only *                                                                              |                                                                                                           |                 |                                                    |  |  |  |

| *periorins a<br>********                                                                                                                       | **performs a byte write, acknowledge polling and finaly a byte read. * ********************************** |                 |                                                    |  |  |  |

| *******                                                                                                                                        |                                                                                                           |                 |                                                    |  |  |  |

| *BIT POSITION EQUATES *                                                                                                                        |                                                                                                           |                 |                                                    |  |  |  |

| ·*************************************                                                                                                         | *******                                                                                                   | ****            |                                                    |  |  |  |

| SDA                                                                                                                                            | BIT                                                                                                       | P1.0            | ;SDA position in port 1                            |  |  |  |

| ~                                                                                                                                              | BIT                                                                                                       |                 | ;SCL position in port 1                            |  |  |  |

| ~                                                                                                                                              |                                                                                                           |                 | ,                                                  |  |  |  |

| •*********<br>'                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

| ;*VARIABL<br>.*********                                                                                                                        |                                                                                                           |                 |                                                    |  |  |  |

| ,                                                                                                                                              |                                                                                                           |                 |                                                    |  |  |  |

| ADDLO                                                                                                                                          | EQU                                                                                                       | R2              | ;low order address pointer                         |  |  |  |

| ADDHI                                                                                                                                          | EQU                                                                                                       | R3              | ;high order address pointer                        |  |  |  |

| COUNT                                                                                                                                          | EQU                                                                                                       | R4              | ;loop counter                                      |  |  |  |

| TDATA<br>RWDATA                                                                                                                                | EQU<br>EQU                                                                                                | R5<br>R6        | ;scratch register<br>;read and write data register |  |  |  |

| KWDAIA                                                                                                                                         | LQU                                                                                                       | KU              | , read and write data register                     |  |  |  |

| ***************************************                                                                                                        |                                                                                                           |                 |                                                    |  |  |  |

| ;*RESET VECTOR *<br>-**********                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

| • ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~                                                                                                        | ****                                                                                                      |                 |                                                    |  |  |  |

| ORG                                                                                                                                            | 0000H                                                                                                     |                 |                                                    |  |  |  |

|                                                                                                                                                | BEGIN                                                                                                     |                 | ;reset vector to address 0100H                     |  |  |  |

| ماه ماه ماه ماه ماه ماه ماه ماه ماه م                                                                                                          | ale ale ale ale ale ale ale ale ale                                                                       | ale ale ale ale |                                                    |  |  |  |

| ;*************************************                                                                                                         |                                                                                                           |                 |                                                    |  |  |  |

| ***********                                                                                                                                    |                                                                                                           |                 |                                                    |  |  |  |

| 7                                                                                                                                              |                                                                                                           |                 |                                                    |  |  |  |

| ORG                                                                                                                                            | 0100H                                                                                                     |                 |                                                    |  |  |  |

| BEGIN:                                                                                                                                         | MOV                                                                                                       | SP,#60H         | ;initialize stack pointer                          |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

|                                                                                                                                                |                                                                                                           |                 |                                                    |  |  |  |

| ;*********<br>;*MAINLINE *<br>;*****                       |                                                                  |                                            |                                                                                                   |  |  |  |

|------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>LCALL<br>LCALL<br>LCALL | A,#023H<br>ADDLO,4<br>A,#096H<br>RWDATA<br>WRITE<br>POLL<br>READ | A<br>A,A                                   | ;write data 96H to address 0123H<br>;perform acknowledge polling<br>;read data from address 0123H |  |  |  |

| DONE: LJI                                                  | MP                                                               | DONE                                       | ;wait until reset loop                                                                            |  |  |  |

| ;*************************************                     |                                                                  |                                            |                                                                                                   |  |  |  |

| ;*************************************                     |                                                                  |                                            |                                                                                                   |  |  |  |

| ,<br>WRITE: LC                                             | ALL                                                              | START                                      | ;issue START condition                                                                            |  |  |  |

| MOV<br>RL                                                  | A,ADDHI<br>A                                                     | [                                          | ;build slave address                                                                              |  |  |  |

|                                                            | A<br>A,#0A0H                                                     |                                            |                                                                                                   |  |  |  |

| LCALL                                                      | SENDB                                                            |                                            | ;send slave address                                                                               |  |  |  |

| LCALL<br>MOV                                               |                                                                  | 2                                          | ;get ACK from NM24C16                                                                             |  |  |  |

| LCALL                                                      |                                                                  | J                                          | ;send low order address                                                                           |  |  |  |

| LCALL                                                      |                                                                  |                                            | ;get ACK from NM24C16                                                                             |  |  |  |

| MOV                                                        | A,RWDA                                                           | ТА                                         |                                                                                                   |  |  |  |

| LCALL<br>LCALL                                             |                                                                  |                                            | ;send data value to write<br>;get ACK from NM24C16                                                |  |  |  |

| LCALL                                                      | STOP                                                             |                                            | ;issue STOP condition                                                                             |  |  |  |

| RET                                                        |                                                                  |                                            | ,                                                                                                 |  |  |  |

| مله                    | ale ale ale ale ale ale ale ale ale                              | the site site site site site site site sit | ٠                                                                                                 |  |  |  |

| ;*************************************                     |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            | ALL                                                              | START                                      | ;issue a START condition                                                                          |  |  |  |

| MOV<br>LCALL                                               | A,#0A0H<br>SENDB                                                 |                                            | ;send the dummy slave address                                                                     |  |  |  |

| LCALL                                                      | ACK                                                              |                                            | ;look for acknowledge from NM24C16                                                                |  |  |  |

| JC                                                         | POLL                                                             |                                            | ;loop until acknowledge is received                                                               |  |  |  |

| LCALL<br>RET                                               | STOP                                                             |                                            | ;issue STOP condition                                                                             |  |  |  |

| NL1                                                        |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            |                                                                  |                                            |                                                                                                   |  |  |  |

|                                                            |                                                                  |                                            |                                                                                                   |  |  |  |

;\*READ perfoms a byte read from the address specified in the ADDHI \* ;\*and ADDLO variables. The data that is read is returned in the ;\*variable RWDATA. \* READ: LCALL START ;issue a START condition MOV A,ADDHI ;issue slave address with R/W=0 RL А ORL A,#0A0H LCALL ;send slave address SENDB LCALL ;get ACK from NM24C16 ACK MOV A, ADDLO LCALL SENDB ;send low order address LCALL ACK ;get ACK from NM24C16 LCALL START ;issue START condition MOV A,ADDHI RL А ORL A,#0A1H LCALL SENDB ;issue slave address with R/W=1 LCALL ;get ACK from NM24C16 ACK LCALL READB ;read data byte MOV RWDATA,A ;put data into RWDATA variable SETB SDA ;clock in a 1 (no acknowledge) LCALL CLOCK LCALL STOP ;issue a STOP condition RET ;\*START issues a START condition to the NM24C16. The routine makes \* ;\*sure that both SDA and SCL are high. Then bring SDA low first \* \* ;\*followed by bringing SCL low. START: SETB SDA ;make sure SDA and SCL are high SETB SCL CLR SDA ;bring SDA low NOP ;NOPs assure correct timing NOP NOP NOP NOP CLR SCL ;bring SCL low RET

;\*STOP issues a STOP condition to the NM24C16. The routine makes \* ;\*sure that the SDA line is low before trying to issue the STOP. \* ;\*The routine then brings SCL high followed by bringing SDA high. \* STOP: SDA CLR ;make sure SDA is low SETB SCL ;bring SCL high NOP ;NOPs assure correct timing NOP NOP NOP NOP SETB SDA ;bring SDA high RET ;\*CLOCK issues a clock pulse to the NM24C16. The state of SDA is \* \* ;\*sampled before the clock pulse is issued. CLOCK: MOV C,SDA ;sample SDA and put state in carry flag SETB SCL ;bring SCL high NOP ;NOPs assure correct timing NOP NOP NOP NOP SCL CLR ;bring SCL low RET ACK allows the NM24C16 to send an acknowledge back to the 8031. \* \*\*\*\*\*\*\*\*\* ACK: SETB SDA ;bring SDA high LCALL CLOCK ;issue a clock pulse RET ;\*SENDB sends a byte to the NM24C16. The routine receives the data \* \* ;\*to send in the A register. SENDB MOV TDATA,A ;move data to send into TDATA MOV A,#8 ;8 bits to send MOV COUNT,A store 8 in down counter MOV ;return data to send into A register A,TDATA NEXTR: RLC ;send most significant bit first Α MOV SDA,C ;move bit to SDA port LCALL CLOCK ;issue clock pulse COUNT,NEXTR ;loop 8 times DJNZ RET

;\*READB reads a byte from the NM24C16. The routine returns the byte \* ;\*that is read in the A register.

;8 bits to read

;loop 8 times

;issue clock pulse

;store 8 in down counter

;store and shift data from SDA

READB: MOV A,#8 MOV COUNT,A NEXTW: LCALL CLOCK RLC A DJNZ COUNT,NEXTW RET

END

## Life Support Policy

Fairchild's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Fairchild Semiconductor Corporation. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Fairchild Semiconductor

Fairchild Semiconductor

Americas

Europe

Customer Response Center

Fax:

+44 (0) 1793-856858

Tel. 1-888-522-5372

Deutsch

Tel:

+49 (0) 8141-6102-0

English

Tel:

+44 (0) 1793-856858

Français

Tel:

+44 (0) 1793-856856

Tel. 1-888-522-5372

Deutsch

Tel:

+44 (0) 1793-856856

Tel. 1-888-522-5372

Tel:

+43 (0) 1693-856856

Français

Tel:

+43 (0) 1693-856856

Français

Tel:

+33 (0) 1693-856856

Français

Tel:

+33 (0) 1693-856856

Fairchild Semiconductor Hong Kong 8/F, Room 808, Empire Centre 68 Mody Road, Tsimshatsui East Kowloon. Hong Kong Tel; +852-2722-8388 Fax: +852-2722-8383 Fairchild Semiconductor Japan Ltd. 4F, Natsume Bldg. 2-18-6, Yushima, Bunkyo-ku Tokyo, 113-0034 Japan Tel: 81-3-3818-8840 Fax: 81-3-3818-8841

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.