# **ORCA<sup>®</sup> Series 4** Field-Programmable Gate Arrays

# Introduction

Built on the Series 4 reconfigurable embedded system-on-chip (SoC) architecture, Agere Systems Inc. introduces its new family of generic field-programmable gate arrays (FPGA). The high-performance and highly versatile architecture brings a new dimension to bringing network system designs to market in less time than ever before. This new device family offers many new features and architectural enhancements not available in any earlier FPGA generations. Bringing together highly flexible SRAM-based programmable logic, powerful system features, a rich hierarchy of routing and interconnect resources, and meeting multiple interface standards, the Series 4 FPGA accommodates the most complex and high-performance intellectual property (IP) network designs.

# **Programmable Features**

- High-performance platform design:

- 0.13 µm 7-level metal technology.

- Internal performance of >250 MHz.

- Meets multiple I/O interface standards.

- 1.5 V operation (30% less power than 1.8 V operation) translates to greater performance.

- Traditional I/O selections:

- LVTTL and LVCMOS (3.3 V, 2.5 V, and 1.8 V) I/Os.

- Per pin-selectable I/O clamping diodes provide 3.3 V PCI compliance.

- Individually programmable drive capability: 24 mA sink/12 mA source, 12 mA sink/6 mA source, or 6 mA sink/3 mA source.

- Two slew rates supported (fast and slew-limited).

- Fast-capture input latch and input flip-flop (FF)/latch for reduced input setup time and zero hold time.

- Fast open-drain drive capability.

- Capability to register 3-state enable signal.

- Off-chip clock drive capability.

- Two-input function generator in output path.

- New programmable high-speed I/O:

- Single-ended: GTL, GTL+, PECL, SSTL3/2 (class I and II), HSTL (Class I, III, and IV), ZBT, and DDR.

- Double-ended: LDVS, bused-LVDS, and LVPECL. Programmable parallel termination (100 Ω) also supported for these I/Os.

| Device | Rows | Columns | PFUs | User I/O | LUTs   | EBR<br>Blocks | EBR Bits<br>(K) | Usable*<br>Gates (K) |

|--------|------|---------|------|----------|--------|---------------|-----------------|----------------------|

| OR4E2  | 26   | 24      | 624  | 400      | 4,992  | 8             | 74              | 260—515              |

| OR4E4  | 36   | 36      | 1296 | 576      | 10,368 | 12            | 111             | 380—800              |

| OR4E6  | 46   | 44      | 2024 | 720      | 16,192 | 16            | 147             | 515—1095             |

Table 1. ORCA Series 4—Available FPGA Logic

\* The usable gate counts range from a logic-only gate count to a gate count assuming 20% of the PFUs/SLICs being used as RAMs. The logic-only gate count includes each PFU/SLIC (counted as 108 gates/PFU), including 12 gates per LUT/FF pair (eight per PFU), and 12 gates per SLIC/FF pair (one per PFU). Each of the four PIO groups are counted as 16 gates (three FFs, fast-capture latch, output logic, CLK, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or 512 gates) per PFU. Embedded block RAM (EBR) is counted as four gates per bit plus each block has an additional 25 K gates. 7 K gates are used for each PLL and 50K gates for the embedded system bus and microprocessor interface logic. Both the EBR and PLLs are conservatively utilized in the gate count calculations.

Note: Devices are not pinout compatible with ORCA Series 2/3.

## Programmable Features (continued)

- New capability to (de)multiplex I/O signals:

- New double data rate on both input and output at rates up to 311 MHz (622 MHz effective rate).

- New 2x and 4x downlink and uplink capability per I/O (i.e., 50 MHz internal to 200 MHz I/O).

- Enhanced twin-quad programmable function unit (PFU):

- Eight 16-bit look-up tables (LUTs) per PFU.

- Nine user registers per PFU, one following each LUT and organized to allow two nibbles to act independently, plus one extra for arithmetic operations.

- New register control in each PFU has two independent programmable clocks, clock enables, local set/reset, and data selects.

- New LUT structure allows flexible combinations of LUT4, LUT5, new LUT6, 4 to 1 MUX, new 8 to 1 MUX, and ripple mode arithmetic functions in the same PFU.

- 32 x 4 RAM per PFU, configurable as single- or dual-port. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the SLIC decoders as bank drivers.

- Soft-wired LUTs (SWL) allow fast cascading of up to three levels of LUT logic in a single PFU through fast internal routing which reduces routing congestion and improves speed.

- Flexible fast access to PFU inputs from routing.

- Fast-carry logic and routing to all four adjacent PFUs for nibble-, byte-wide, or longer arithmetic functions, with the option to register the PFU carry-out.

- Abundant high-speed buffered and nonbuffered routing resources provide 2x average speed improvements over previous architectures.

- Hierarchical routing optimized for both local and global routing with dedicated routing resources. This results in faster routing times with predictable and efficient performance.

- SLIC provides eight 3-statable buffers, up to 10-bit decoder, and PAL\*-like and-or-invert (AOI) in each programmable logic cell.

- Improved built-in clock management with programmable phase-locked loops (PPLLs) provide optimum clock modification and conditioning for phase, frequency, and duty cycle from 20 MHz up to 420 MHz.

- New 200 MHz embedded quad-port RAM blocks, two read ports, two write ports, and two sets of byte lane enables. Each embedded RAM block can be configured as:

- 1-512 x 18 (quad-port, two read/two write) with optional built in arbitration.

- 1-256 x 36 (dual-port, one read/one write).

- 1-1K x 9 (dual-port, one read/one write).

- 2-512 x 9 (dual-port, one read/one write for each).

- 2 RAMS with arbitrary number of words whose sum is 512 or less by 18 (dual-port, one read/one write).

- Supports joining of RAM blocks.

- Two 16 x 8-bit content addressable memory (CAM) support.

- FIFO 512 x 18, 256 x 36, 1K x 9 or dual 512 x 9.

- Constant multiply (8 x 16 or 16 x 8).

- Dual-variable multiply (8 x 8).

- Embedded 32-bit internal system bus plus 4-bit parity interconnects FPGA logic, microprocessor interface (MPI), embedded RAM blocks, and embedded standard cell blocks with 100 MHz bus performance. Included are built-in system registers that act as the control and status center for the device.

- Built-in testability:

- Full boundary scan (*IEEE*<sup>†</sup>1149.1 and Draft 1149.2 joint test access group (JTAG)).

- Programming and readback through boundary scan port compliant to *IEEE* Draft 1532:D1.7.

- TS\_ALL testability function to 3-state all I/O pins.

- New temperature sensing diode.

- New cycle stealing capability allows a typical 15% to 40% internal speed improvement after final place and route. This feature also enables compliance with many setup/hold and clock-to-out I/O specifications and may provide reduced ground bounce for output buses by allowing flexible delays of switching output buffers.

† *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

<sup>\*</sup> PAL is a trademark of Advanced Micro Devices, Inc.

# **System Features**

- PCI local bus compliant.

- Improved PowerPC\*860 and PowerPC II high-speed synchronous microprocessor interface can be used for configuration, readback, device control, and device status, as well as for a general-purpose interface to the FPGA logic, RAMs, and embedded standard cell blocks. Glueless interface to synchronous PowerPC processors with user-configurable address space provided.

- New embedded AMBA<sup>†</sup> specification 2.0 AHB system bus (ARM<sup>†</sup> processor) facilitates communication among the microprocessor interface, configuration logic, embedded block RAM, FPGA logic, and embedded standard cell blocks.

- New network PLLs meet ITU-T G.811 specifications and provide clock conditioning for DS-1/E-1 and STS-3/STM-1 applications.

- Flexible general purpose PPLLs offer clock multiply (up to 8x), divide (down to 1/8x), phase shift, delay compensation, and duty cycle adjustment combined.

- Variable size bused readback of configuration data capability with the built-in microprocessor interface and system bus.

- Internal, 3-state, bidirectional buses with simple control provided by the SLIC.

- New clock routing structures for global and local clocking significantly increases speed and reduces skew (<200 ps for OR4E4).</li>

- New local clock routing structures allow creation of localized clock trees.

- New double-data rate (DDR) and zero-bus turnaround (ZBT) memory interfaces support the latest high-speed memory interfaces.

- New 2x/4x uplink and downlink I/O capabilities interface high-speed external I/Os to reduced speed internal logic.

- Meets universal test and operations PHY interface for ATM (UTOPIA) Levels 1, 2, and 3. Also meets proposed specifications for UTOPIA level 4, POS-PHY Level 3 (2.5 Gbits/s), and POS-PHY 4 (10 Gbits/s) interface standards for packet-over-SONET as defined by the Saturn Group.

- ORCA Foundry 2000 development system software. Supported by industry-standard CAE tools for design entry, synthesis, simulation, and timing analysis.

- Two new edge clock routing structures allow up to seven high-speed clocks on each edge of the device for improved setup/hold and clock to out performance.

### **Intellectual Property Features**

Programmable logic provides the ability to implement a variety of interface functions before they have been completely standarized. Agere is the leading provider of networking devices and can supply a large number of networking IP cores targeted to *ORCA* FPGAs. Contact your local Agere sales representitive for more information.

- \* *PowerPC* is a registered trademark of International Business Machines, Inc.

- † AMBA and ARM are trademarks of Advanced RISC Machines, Limited.

## System Features (continued)

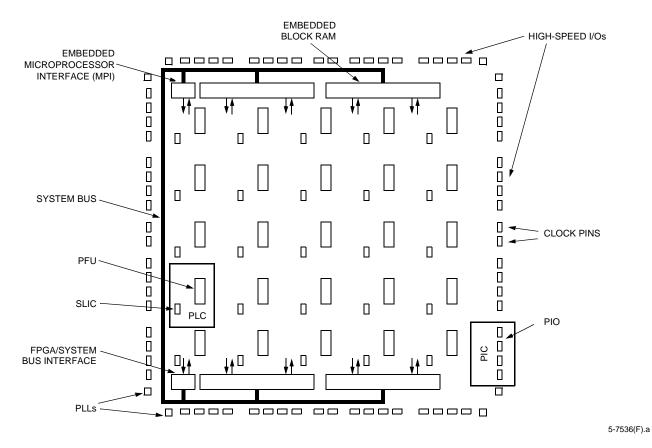

Figure 1. Series 4 FPGA Block Diagram

# **Ordering Information**

5-6435 (F).I

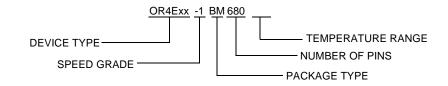

### Figure 2. OR4Exx, -1 Speed Grade, 680-pin Plastic Ball Grid Array Multilayer (PBGAM)

### Table 2. Device Type Options

| Device | Voltage        |  |  |

|--------|----------------|--|--|

| OR4Exx | 1.5 V internal |  |  |

### Table 3. Temperature Options

| Symbol  | Description | Temperature      |  |  |

|---------|-------------|------------------|--|--|

| (Blank) | Industrial  | –40 °C to +85 °C |  |  |

### Table 4. Package Options

| Symbol | Description                                 |  |

|--------|---------------------------------------------|--|

| BA     | Plastic Ball Grid Array (PBGA)              |  |

| BC     | Enhanced Ball Grid Array (EBGA)             |  |

| BM     | Plastic Ball Grid Array, Multilayer (PBGAM) |  |

#### Table 5. ORCA OR4EXX Series Package Matrix (Speed Grade)

| Devices | 256-Pin<br>PBGA | 352-Pin<br>PBGA | 416-Pin<br>PBGAM | 432-Pin<br>EBGA | 680-Pin<br>PBGAM |

|---------|-----------------|-----------------|------------------|-----------------|------------------|

| OR4E2   | -1, -2, -3      | -1, -2, -3      | -1, -2, -3       | —               | -1, -2, -3       |

| OR4E4   |                 | -1, -2, -3      | -1, -2, -3       | -1, -2, -3      | -1, -2, -3       |

| OR4E6   |                 | -1, -2, -3      | —                | -1, -2, -3      | -1, -2, -3       |

For additional information, contact your Agere Systems Account Manager or the following: http://www.agere.com or for FPGAs/FPSCs: http://www.agere.com/orca INTERNET: E-MAIL: docmaster@micro.lucent.com N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495 CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC Tel. (86) 21 50471212, FAX (86) 21 50472266 JAPAN: Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 Data Requests: DATALINE: Tel. (44) 700 582 368, FAX (44) 1189 328 148 Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), EUROPE: FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki), ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. ORCA is a registered trademark of Agere Systems Inc. Foundry is a trademark of Xilinx.

Copyright © 2001 Agere Systems Inc. All Rights Reserved Printed in U.S.A.