**July 1997**

## Description

NEC's CMOS-9 gate array family provides designers with the performance capabilities and features required to develop devices for high-speed computer and communications systems. NEC combines the highest performance 0.35-micron drawn gate length (Leff=0.27 micron) 2- and 3-level metal CMOS technology with an extensive family of interface macros to support very high-speed system clocks. The high performance I/O macros including GTL, HSTL, and pECL are under development. PCI signaling standards are also supported including 3.3V 66 MHz PCI.

This technology is enhanced by a set of advanced features including phase-locked loops, clock tree synthesis, and high-speed memory.

The CMOS-9 gate array family of 3.3-volt devices consists of 20 masters, offered in densities of 190K raw gates to 2 million raw gates. Usable gates range from 76K to 1.2 million used gates.

The gate array family is supported by NEC's OpenCAD® design system; a mixture of popular third-party CAE tools, and proprietary NEC tools. NEC proprietary tools include the GALET floorplanner which helps reduce design cycle time and improve design performance, clock tree synthesis for clock skew minimization, and table look-up delay calculator for accurate delay calculation.

Figure 1. CMOS-9 Package Examples; BGA and QFP

# **CMOS-9 Applications**

The CMOS-9 family is ideal for use in enterprise systems, engineering workstations, telecommunications switching and transmission systems, where extensive integration and high speeds are primary design goals. CMOS-9 is well-suited for designs requiring very high integration (300K-600K gates, 400-600 pins), high system speeds (100-200 MHz), and high performance interface standards (HSTL, GTL). CMOS-9 is also well-suited for lower power applications where high performance is required. CMOS-9 is offered now at 3.3V and will be released at 2.5V in the future.

Table 1. CMOS-9 Series Features and Benefits

| CMOS-9 Series Features                                   | CMOS-9 Series Benefits                                     |

|----------------------------------------------------------|------------------------------------------------------------|

| 0.35-micron (drawn), 2 and 3-level metal CMOS technology | Delivers dense cell structure and high speed               |

| Eighteen base arrays with raw gates from 190K to 1.5M    | Provides many base sizes to give best fit to design needs  |

| Narrow pad pitch for maximum gate to pad ratio           | Minimizes device cost                                      |

| Pad counts from 300 to 1060 pads                         | Supports high I/O integration and wide system bus widths   |

| GTL, GTL+, pECL, and all four classes of HSTL            | Interfaces to high speed memory and processor buses        |

| Full range of 5V-protected I/O buffers                   | Allows interface with 5V logic while protecting 3.3V ASIC  |

| PCI buffers including 3.3V 66 MHz PCI buffer             | Supports signaling methods defined in PCI Spec 2.1         |

| Phase-Locked Loop (DPLL) macros in development           | Eliminates clock insertion delay, reduces total clock skew |

| Low power dissipation: 0.9 μW/MHz/gate                   | Provides low power consumption at high system clock rates  |

| Extensive package offering: PQFP, TQFP, BGA, TAB         | Delivers customer-specific package requirements            |

| Clock Tree Synthesis tool automates clock tree design    | Minimizes on-chip clock skew for high performance          |

| Floorplanner supplies layout information for resynthesis | Reduces design time and improves device performance        |

| Popular, third-party CAE tools supported                 | Enables a smooth flow from customer design to silicon      |

## Array Architecture

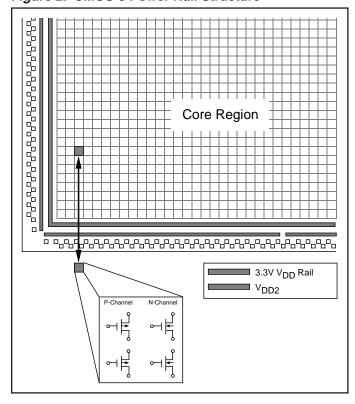

The CMOS-9 gate array family is built with NEC's 0.35-micron (drawn) channelless array architecture. As shown in Figure 2, the array is divided into I/O and core regions. The I/O region contains input and output buffers. The core region contains the sea-of-gates array.

The CMOS-9 gate arrays architecture provides extra flexibility for high performance system designs. As shown in Figure 2, the arrays contain two power rails: a 3.3V rail, and a second power rail (V<sub>DD2</sub>) for special I/O types.

The  $V_{DD2}$  rail is used for interfaces such as HSTL where a very low I/O power supply is required (1.4 to 1.6V). All four classes of HSTL buffer are supported.

The  $V_{DD2}$  rail may be separated into sections to allow one device to support two or more busses requiring special I/O voltages. Examples of spread I/O cells that may use this  $V_{DD}$  rail are HSTL and 5V PCI. Each section can operate as an independent voltage zone, and sections can be linked together to form common voltage zones.

#### Core Architecture

The core region consists of an array of gates. Each gate contains 2 n-channel and 2 p-channel MOS logic transistors. One core gate is equivalent to one 2-input NAND gate (L302). The logic transistors are sized to offer a superior ratio of speed to silicon area.

Table 2. CMOS-9 Base Array Line-up

|    | _                                   |                    |               |                             |                           |                       |

|----|-------------------------------------|--------------------|---------------|-----------------------------|---------------------------|-----------------------|

|    | ice <sup>(1)</sup><br>659xx)<br>3LM | Available<br>Gates | Usable<br>2LM | Gates <sup>(2)</sup><br>3LM | Max P<br>Regular<br>Pitch | ads<br>Tight<br>Pitch |

| 06 | 26                                  | 190152             | 76061         | 114091                      | 300                       | 388                   |

| 07 | 27                                  | 249948             | 99979         | 149969                      | 340                       | 444                   |

| 08 | 28                                  | 317904             | 127162        | 190742                      | 380                       | 500                   |

| 09 | 29                                  | 376740             | 150696        | 226044                      | 412                       | 540                   |

| 10 | 30                                  | 462088             | 184835        | 277253                      | 452                       | 596                   |

| 11 | 31                                  | 629824             | 251930        | 377894                      | 524                       | 692                   |

| 13 | 33                                  | 805580             | 322232        | 483348                      | 588                       | 772                   |

| 15 | 35                                  | 1076032            | 430413        | 645619                      | 676                       | 892                   |

| 17 | 37                                  | 1545240            | 618096        | 927144                      | 804                       | 1060                  |

<sup>(1) 2</sup>LM represents two-layer metal; 3LM represents three-layer metal.

Figure 2. CMOS-9 Power Rail Structure

## **Packaging and Test**

CMOS-9 gate arrays support automatic test generation through a scan-test methodology, which allows higher fault coverage, easier testing and quicker development time. NEC also offers optional BIST test structures for RAM testing.

NEC offers advanced packaging solutions including Ball Grid Arrays (BGA), Plastic Quad Flat Packs (PQFP), Low Profile Plastic Quad Flat Packs (LQFP), Thin Plastic Quad Flat Packs (TQFP), Pin Grid Arrays (PGA) and advanced TAB technology.

Please contact your local NEC ASIC Design Center for a listing of available master/package combinations.

### **Publications**

This data sheet contains preliminary specifications, package information, and operational data for the CMOS-9 gate array family. Additional design information will be available in NEC's CMOS-9 Block Library and CMOS-9 Design Manual.

Contact your local NEC ASIC Design Center or the NEC Literature Center for further ASIC design information; see the back of this data sheet for locations and phone numbers.

<sup>(2)</sup> Actual gate utilization varies depending on circuit implementation. Utilization is 40% for 2LM; 60% for 3LM.

## **Absolute Maximum Ratings**

| Power supply voltage, $V_{\rm DD}$                           | -0.5 to +4.6 V |

|--------------------------------------------------------------|----------------|

| Input voltage, V <sub>I</sub>                                |                |

| 3V Input buffer (at $V_I < V_{DD} + 0.5V$ )                  | -0.5 to 4.6 V  |

| $3V$ Fail-safe input buffer (at $V_1 < V_{DD} + 0.5V$ )      | -0.5 to 4.6 V  |

| 5V Input buffer (at V <sub>I</sub> < V <sub>DD</sub> + 0.5V) | -0.5 to 6.6 V  |

| Output voltage, V <sub>O</sub>                               |                |

| $3V$ Output buffer (at $V_O < V_{DD} + 0.5V$ )               | -0.5 to 4.6 V  |

| 5V TTL Output buffer (at $V_O < V_{DD} + 3.0V$ )             | -0.5 to 6.6 V  |

| 5V CMOS Output buffer (at $V_O < V_{DD} + 3.0V$ )            | -0.5 to 6.6 V  |

| Latch-up current, I <sub>LATCH</sub>                         | >1 A (typ)     |

| Operating temperature, T <sub>OPT</sub>                      | -40 to +85°C   |

| Storage temperature, T <sub>STG</sub>                        | -65 to +150°C  |

# **Input/Output Capacitance**

$V_{DD} = V_{I} = 0 \text{ V}; f = 1 \text{ MHz}$

| Termina | al | Symbol           | MIn | Тур | Max  | Unit |

|---------|----|------------------|-----|-----|------|------|

| Innut   | 3V | C                | 4.0 |     | 6.0  | pF   |

| Input   | 5V | $C_{IN}$         | 8.0 |     | 10.0 | ρг   |

| Output  | 3V | <u> </u>         | 4.0 |     | 6.0  | pF   |

| Output  | 5V | C <sub>OUT</sub> | 8.0 |     | 10.0 | ρг   |

| 1/0     | 3V | C                | 4.0 |     | 6.0  | n.E  |

| I/O     | 5V | C <sub>I/O</sub> | 8.0 |     | 10.0 | pF   |

<sup>1)</sup> Values include package pin capacitance.

## **Power Consumption**

| Description                  | Limits | Unit   |

|------------------------------|--------|--------|

| Internal gate                | 1.09   | μW/MHz |

| Input buffer (FI01)          | 15.05  | μW/MHz |

| Output buffer (FO01 @ 15 pF) | 234    | μW/MHz |

**Caution:** Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.

# **Recommended Operating Conditions**

|                               |                                 | 3.3V Interface<br>Block |                 | 5V Interface<br>Block |      | 5V PCI<br>Level |                 | 3.3V PCI<br>Level  |                    |      |  |

|-------------------------------|---------------------------------|-------------------------|-----------------|-----------------------|------|-----------------|-----------------|--------------------|--------------------|------|--|

| Parameter                     | Symbol                          | Min                     | Max             | Min                   | Max  | Min             | Max             | Min                | Max                | Unit |  |

| I/O Power supply voltage      | V <sub>DD</sub>                 | 3.0                     | 3.6             | 3.0                   | 3.6  | 3.0             | 3.6             | 3.0                | 3.6                | V    |  |

| Junction temperature          | T <sub>J</sub>                  | -40                     | +125            | -40                   | +125 | -40             | +125            | -40                | +125               | °C   |  |

| High-level input voltage      | V <sub>IH</sub>                 | 2.0                     | V <sub>DD</sub> | 2.0                   | 5.5  | 2.0             | V <sub>CC</sub> | 0.5V <sub>CC</sub> | V <sub>CC</sub>    | V    |  |

| Low-level input voltage       | V <sub>IL</sub>                 | 0                       | 0.8             | 0                     | 0.8  | 0               | 0.8             | 0                  | 0.3V <sub>CC</sub> | V    |  |

| Positive trigger voltage      | V <sub>P</sub>                  | 1.5                     | 2.7             | 2.2                   | 2.55 | T -             | _               | _                  | _                  | V    |  |

| Negative trigger voltage      | V <sub>N</sub>                  | 0.6                     | 1.4             | 0.84                  | 1.01 | T -             | _               | _                  | _                  | V    |  |

| Hysteresis voltage            | V <sub>H</sub>                  | 1.1                     | 1.5             | 1.36                  | 1.54 | _               | _               | _                  | _                  | V    |  |

| Input rise/fall time          | t <sub>R</sub> , t <sub>F</sub> | 0                       | 200             | 0                     | 200  | 0               | 200             | 0                  | 200                | ns   |  |

| Input rise/fall time, Schmitt | t <sub>R</sub> , t <sub>F</sub> | 0                       | 10              | 0                     | 10   | -               | _               | _                  | _                  | ns   |  |

# **AC Characteristics**

$V_{DD} = 3.3V \pm 0.3V; T_j = -40 \text{ to } +125^{\circ}\text{C}$

| Parameter                          | Symbol           | Min | Тур  | Max | Unit | Conditions             |

|------------------------------------|------------------|-----|------|-----|------|------------------------|

| Toggle frequency (D-flip-flop)     | f <sub>TOG</sub> |     |      | 670 | MHz  | F/O = 2, 5V            |

| Delay time, 2-input NAND gate @ 5V |                  |     |      |     |      |                        |

| Standard gata (E202)               |                  |     | 99   |     | ps   | F/O = 1; L = 0 mm      |

| Standard gate (F302)               | t <sub>PD</sub>  |     | 150  |     | ps   | F/O = 2; L = 0.5 mm    |

| Paragraph (F000)                   | 4                |     | 84   |     | ps   | F/O = 1; $L = 0  mm$   |

| Power gate (F322)                  | t <sub>PD</sub>  |     | 119  |     | ps   | F/O = 2; L = 0.5 mm    |

| Delay time, buffer                 |                  |     |      |     |      |                        |

| Input buffer (FI01)                | t <sub>PD</sub>  |     | 188  |     | ps   | F/O = 1; $L = 0.5  mm$ |

| Input buffer (FI01)                | t <sub>PD</sub>  |     | 216  |     | ps   | F/O = 2; L = 0 mm      |

| Output buffer (FO01)               | t <sub>PD</sub>  |     | 1.40 |     | ns   | C <sub>L</sub> = 15 pF |

| Output rise time (FO01)            | t <sub>R</sub>   |     | 2.35 |     | ns   | C <sub>L</sub> = 15 pF |

| Output fall time (FO01)            | t <sub>F</sub>   |     | 1.83 |     | ns   | C <sub>L</sub> = 15 pF |

### **DC Characteristics**

$V_{DD} = 3.3V \pm 0.3V$ ;  $T_i = -40 \text{ to } +125^{\circ}\text{C}$

| Parameter                                        | Symbol                             | Min                  | Тур               | Max   | Unit     | Conditions                                           |

|--------------------------------------------------|------------------------------------|----------------------|-------------------|-------|----------|------------------------------------------------------|

| Quiescent current (µPD659xx) (1)                 |                                    |                      |                   |       |          |                                                      |

| -19, -39                                         | Ι <sub>L</sub>                     |                      | 7                 | 1400  | μA       | $V_I = V_{DD}$ or GND                                |

| -17, -37, -15, -35, -13, -33, -11, -31           | $I_{L}$                            |                      | 4                 | 800   | μΑ       | $V_I = V_{DD}$ or GND                                |

| -10, -30, -09, -29, -08, -28                     | IL                                 |                      | 2                 | 400   | μΑ       | $V_I = V_{DD}$ or GND                                |

| -06, -26, -07, -27                               | IL                                 |                      | 1                 | 200   | μΑ       | $V_I = V_{DD}$ or GND                                |

| Off-state output leakage current                 |                                    |                      |                   |       |          |                                                      |

| 3V output buffer                                 | I <sub>OZ</sub>                    |                      |                   | ±10   | μA       | $V_O = V_{DD}$ or GND                                |

| 5V-protected TTL buffer                          | $I_{OZ}$                           |                      |                   | ±10   | μΑ       | $V_O = V_{DD}$ or GND                                |

| Output short circuit current (3)                 | I <sub>os</sub>                    |                      |                   | -250  | mA       | V <sub>O</sub> = GND                                 |

| Input leakage current (2)                        |                                    |                      |                   |       |          |                                                      |

| Regular                                          | I <sub>I</sub>                     |                      | ±10 <sup>-4</sup> | ±10   | μA       | $V_I = V_{DD}$ or GND                                |

| 50 k $\Omega$ pull-up                            | I <sub>I</sub>                     | 36                   | 89                | 165   | μΑ       | $V_I = GND$                                          |

| 5 k $\Omega$ pull-up                             | I <sub>I</sub>                     | 284                  | 654               | 1305  | μΑ       | $V_I = GND$                                          |

| 50 k $\Omega$ pull-down                          | I <sub>I</sub>                     | 28                   | 79                | 141   | μA       | $V_I = V_{DD}$                                       |

| Resistor values                                  |                                    |                      |                   |       |          |                                                      |

| 50 kΩ pull-up (4)                                | R <sub>pu</sub>                    | 21.8                 | 37.1              | 83.1  | kΩ       |                                                      |

| 5 kΩ pull-up                                     | R <sub>pu</sub>                    | 2.8                  | 5.0               | 10.6  | kΩ       |                                                      |

| 50 kΩ pull-down                                  | R <sub>pu</sub>                    | 25.6                 | 41.9              | 105.8 | kΩ       |                                                      |

| Low-level output current (5V Interface block)    | ρū                                 |                      |                   |       |          |                                                      |

| 1 mA                                             | I <sub>OL</sub>                    | 1                    |                   |       | mA       | V <sub>OL</sub> = 0.4 V                              |

| 2 mA                                             | I <sub>OL</sub>                    | 2                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 3 mA                                             | I <sub>OL</sub>                    | 3                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 6 mA                                             | I <sub>OL</sub>                    | 6                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 9 mA                                             | I <sub>OL</sub>                    | 9                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 12 mA                                            | I <sub>OL</sub>                    | 12                   |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| High-level output current (5V Interface block)   | <u> </u>                           |                      |                   |       |          | OL .                                                 |

| 1 mA                                             | I <sub>OH</sub>                    | -1                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 2 mA                                             | I <sub>OH</sub>                    | -1                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 3 mA                                             | I <sub>OH</sub>                    | -3                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 6 mA                                             | I <sub>OH</sub>                    | -3                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 9 mA                                             | I <sub>OH</sub>                    | -3                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 12 mA                                            | I <sub>OH</sub>                    | -3                   |                   |       | mA       | $V_{OH} = 2.4 \text{ V}$                             |

| Low-level output current (3.3V Interface block)  | •ОН                                |                      |                   |       |          | *OH =:: *                                            |

| 3 mA (FO09)                                      | I <sub>OL</sub>                    | 3                    |                   |       | mA       | V <sub>OL</sub> = 0.4 V                              |

| 6 mA (FO04)                                      | I <sub>OL</sub>                    | 6                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 9 mA (FO01)                                      | I <sub>OL</sub>                    | 9                    |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 12 mA (FO02)                                     | I <sub>OL</sub>                    | 12                   |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 18 mA (FO03)                                     |                                    | 18                   |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$                             |

| 24 mA (FO06)                                     | I <sub>OL</sub><br>I <sub>OL</sub> | 24                   |                   |       | mA       | $V_{OL} = 0.4 \text{ V}$<br>$V_{OL} = 0.4 \text{ V}$ |

| High-level output current (3.3V Interface block) | 'OL                                | <u></u>              |                   |       | 111/1    | V OL − 0.7 V                                         |

| 3 mA (FO09)                                      | lo::                               | -3                   |                   |       | mA       | V <sub>OH</sub> = 2.4 V                              |

| 6 mA (FO04)                                      | I <sub>OH</sub>                    | -5<br>-6             |                   |       | mA       | $V_{OH} = 2.4 \text{ V}$<br>$V_{OH} = 2.4 \text{ V}$ |

| 9 mA (FO01)                                      | I <sub>OH</sub>                    | -9                   |                   |       | mA       | $V_{OH} = 2.4 \text{ V}$<br>$V_{OH} = 2.4 \text{ V}$ |

|                                                  | I <sub>OH</sub>                    | -9<br>-12            |                   |       |          |                                                      |

| 12 mA (FO02)<br>18 mA (FO03)                     | I <sub>OH</sub>                    | -12<br>-18           |                   |       | mA<br>m^ | $V_{OH} = 2.4 \text{ V}$                             |

| ,                                                | I <sub>OH</sub>                    |                      |                   |       | mA<br>m^ | $V_{OH} = 2.4 \text{ V}$                             |

| 24 mA (FO06)                                     | I <sub>OH</sub>                    | -24                  |                   | 0.4   | mA<br>V  | V <sub>OH</sub> = 2.4 V                              |

| Low-level output voltage                         | V <sub>OL</sub>                    | V 0.4                |                   | 0.1   |          | $I_{OL} = 0 \text{ mA}$                              |

| High-level output voltage                        | $V_{OH}$                           | V <sub>DD</sub> -0.1 |                   |       | V        | I <sub>OH</sub> = 0 mA                               |

#### Notes:

- (1) Static current consumption increases if an I/O block with on-chip pull-up/pull-down resistor or an oscillator is used. Contact an NEC ASIC Design Center for assistance in calculation.

- (2) Leakage current is limited by tester capabilities. Specification listed represents this measurement limitation. Actual values will be significantly lower.

- (3) Rating is for only one output operating in this mode for less than 1 second.

- (4) Resistor is called  $50k\Omega$  for backwards compatibility.

## **CAD Support**

The CMOS-9 family is fully supported by NEC's sophisticated OpenCAD design framework, CMOS-9 maximizes design quality and flexibility while minimizing ASIC design time.

NEC's OpenCAD system allows designers to combine the EDA industry's most popular third-party design tools with proprietary NEC tools, including those for advanced floorplanner, clock tree synthesis, automatic test pattern generation (ATPG), full-timing simulation, accelerated fault grading and advanced place and route algorithms. The latest OpenCAD system is open for sign-off using standard EDA tools. NEC offers RTL- and STA- (Static Timing Analysis) sign-off procedures to shorten the ASIC design cycle of high-complexity designs.

Support of High-Speed Systems. High-speed systems require tight control of clock skew on the chip and between devices on a printed circuit board. CMOS-9 provides three features to control clock skew: the standard Digital PLL (DPLL) working at frequencies up to 100 MHz for chip-to-chip skew minimization, the multiplying digital PLL providing frequencies up to 200 MHz, and Clock Tree Synthesis (CTS). CTS — supported by an NEC proprietary design tool — is used for clock skew management through the automatic insertion of a balanced buffer tree. The clock tree insertion method minimizes large-capacitive trunks and is especially useful with the hierarchical, synthesized design style being used for high-integration devices. RC values for actual net lengths of the clock tree are used for back annotation after place and route operations. A skew as low as ±100 ps can be achieved.

Accurate Design Verification. Nonlinear timing calculation is a very important requirement of the high-density, deep sub-micron ASIC designs. NEC makes use of the increased accuracy delivered by the nonlinear table look-up delay calculation methodology and offers consistent wire load models to ensure a high accuracy of the design verification.

**Design Rule Check.** A comprehensive design rule check (DRC) program reports design rule violations as well as chip utilization statistics for the design netlist. The generated report contains such information as net counts, total pin and gate counts, and utilization figures.

Layout. During design synthesis, wire load models are used to get delay estimations in a very early state of the design flow. In general, there's no need for customers to perform the floorplanning to meet the required timing. During layout, enhanced in-place optimization (IPO) features of the layout tools and engineering change order (ECO) capabilities of the synthesis tools are used to optimize critical timing paths defined by the given timing constraints. This feature can reduce the total design time.

### **Test Support**

The CMOS-9 family supports automatic test generation through a scan test methodology. It includes internal scan, boundary scan (JTAG) and built-in-self-test (BIST) architecture for easy and high-performance production RAM testing. This allows higher fault coverage, easier testing and faster development time.

## **NEC ASIC DESIGN CENTERS**

#### **WEST**

3033 Scott Boulevard Santa Clara, CA 95054

TEL 408-588-5008 FAX 408-588-5017

One Embassy Centre 9020 S.W. Washington Square Road, Suite 400 Tigard, OR 97223

TEL 503-671-0177 FAX 503-643-5911

#### SOUTH CENTRAL/SOUTHEAST

Three Galleria Tower 13155 Noel Road, Suite 1100 Dallas, TX 75240

TEL 972-855-5150 FAX 972-503-3993

Research Triangle Park 2000 Regency Parkway, Suite 455 Cary, NC 27511

TEL 919-460-1890 FAX 919-469-5926

Two Chasewood Park 20405 SH 249, Suite 580 Houston, TX 77070

TEL 713-320-0524 FAX 713-320-0574

### NORTH CENTRAL/NORTHEAST

The Meadows, 2nd Floor 161 Worcester Road Framingham, MA 01701

TEL 508-935-2200 FAX 508-935-2234

Greenspoint Tower

2800 W. Higgins Road, Suite 765

Hoffman Estates, IL 60195

TEL 708-519-3945 FAX 708-882-7564

### THIRD-PARTY DESIGN CENTERS

### SOUTH CENTRAL/SOUTHEAST

Koos Technical Services, Inc. 385 Commerce Way, Suite 101 Longwood, FL 32750

TEL 407-260-8727 FAX 407-260-6227

Integrated Silicon Systems Inc. 2222 Chapel Hill Nelson Highway Durham, NC 27713

TEL 919-361-5814 FAX 919-361-2019

Applied Systems, Inc. 1761 W. Hillsboro Blvd., Suite 328 Deerfield Beach, FL 33442

TEL 305-428-0534 FAX 305-428-5906

For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: **1-800-366-9782** or FAX your request to: **1-800-729-9288**

NEC Electronics Inc.

**CORPORATE HEADQUARTERS**

2880 Scott Boulevard P.O. Box 58062 Santa Clara, CA 95052 TEL 408-588-6000 No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INICUDING THE LIMITATION OF LIABILITY, WAR-RANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL's willingness to support a given application.