# 2Mx64 3.3V Simultaneous Operation Multi-Chip Package \*Preliminary

# **FEATURES**

- Access Times of 70, 100, 120, 150ns

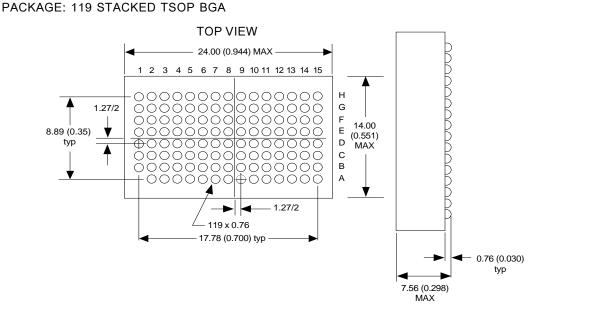

- Packaging

- · 119 ball stacked TSOP BGA

- 1,000,000 Erase/Program Cycles

- Sector Architecture

- 252 32K word sectors and 32 4K word sectors

- Any combination of sectors can be concurrently erased. Also supports full chip erase

- Organized as 2Mx64

- Commercial, Industrial and Military Temperature Ranges

- 3.3 Volt for Read and Write Operations

- Simultaneous Read/Write Operation

- Data can be continuously read from one bank while executing erase/program functions in other banks

- Embedded Erase and Program Algorithms

- Erase Suspend/Resume

- Supports reading data from or programing data to a sector not being erased

- Data Polling and Toggle Bits

- Provides a software method of detecting the status of program or erase cycles

- Unlock Bypass Program command

- Reduces overall programming time when issuing multiple program command sequences

- Ready/Busy output (RY/BY)

- Hardware method for detecting program or erase cycle completion

- Hardware reset pin (RESET)

- Hardware method of resetting the internal state machine to the read mode

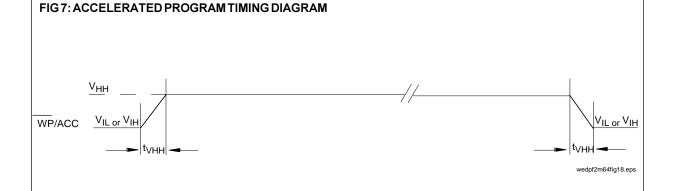

- WP/ACC input pin

- Write protect (WP) function allows protection of two outermost boot sectors, regardless of sector protect status

- Acceleration (ACC) function accelerates program timing

- Sector Protection

- Hardware method of locking a sector, either in-system or using programming equipment, to prevent any program or erase operation within that sector

- Temporary Sector Unprotect allows changing data in protected sectors in-system

Note: For programming information refer to Flash Programming WEDPF2M64-XXX3 Application Note.

<sup>\*</sup> Preliminary datasheet. This datasheet describes a product that is not fully qualified or characterized and is subject to change without notice.

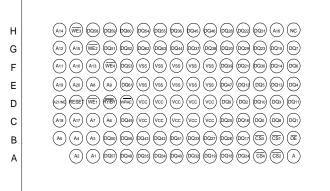

# FIG 1: PIN CONFIGURATION FOR WEDPF2M64-XBX3

### **TOP VIEW**

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

wedpf2m64-xbx3pc.eps

### PIN DESCRIPTION

| I/O <sub>0-63</sub> | Data Inputs/Outputs |

|---------------------|---------------------|

| A0-20               | Address Inputs      |

| WE1-4               | Write Enables       |

| CS <sub>1-4</sub>   | Chip Selects        |

| ŌĒ                  | Output Enable       |

| RESET               | Reset/Powerdown     |

| Vcc                 | Power Supply        |

| Vss                 | Ground              |

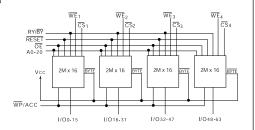

### **BLOCK DIAGRAM**

### ABSOLUTE MAXIMUM RATINGS

| Parameter                      |                  | Unit   |

|--------------------------------|------------------|--------|

| Operating Temperature          | -55 to +125      | °C     |

| Supply Voltage Range (Vcc)     | -0.5 to +4.0     | V      |

| Signal Voltage Range           | -0.5 to Vcc +0.5 | V      |

| Storage Temperature Range      | -65 to +150      | °C     |

| Endurance (write/erase cycles) | 1,000,000 min.   | cycles |

#### NOTES:

1. Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

### RECOMMENDED OPERATING CONDITIONS

| Parameter              | Symbol | Min       | Max       | Unit |

|------------------------|--------|-----------|-----------|------|

| Supply Voltage         | Vcc    | 3.0       | 3.6       | V    |

| Input High Voltage     | ViH    | 0.7 x Vcc | Vcc + 0.3 | V    |

| Input Low Voltage      | VIL    | -0.5      | +0.8      | V    |

| Operating Temp. (Mil.) | TA     | -55       | +125      | °C   |

| Operating Temp. (Ind.) | TA     | -40       | +85       | °C   |

### **CAPACITANCE**

$(TA = +25^{\circ}C)$

| Parameter                     | Symbol | Conditions                         | Max | Unit |

|-------------------------------|--------|------------------------------------|-----|------|

| WE <sub>1-4</sub> capacitance | Cwe    | VIN = 0 V, f = 1.0 MHz             | 8   | pF   |

| CS <sub>1-4</sub> capacitance | Ccs    | V <sub>IN</sub> = 0 V, f = 1.0 MHz | 10  | pF   |

| Data I/O capacitance          | Cı/o   | Vvo = 0 V, f = 1.0 MHz             | 12  | pF   |

| Address input capacitance     | CAD    | V <sub>IN</sub> = 0 V, f = 1.0 MHz | 25  | pF   |

| RESET capacitance             | Crs    | V <sub>IN</sub> = 0 V, f = 1.0 MHz | 20  | pF   |

| RY/BY capacitance             | Спв    | V <sub>IN</sub> = 0 V, f = 1.0 MHz | 20  | pF   |

| WP/AC capacitance             | CWA    | V <sub>IN</sub> = 0 V, f = 1.0 MHz | 30  | pF   |

This parameter is guaranteed by design but not tested.

### **DATA RETENTION**

| Parameter            | Test Conditions | Min | Unit  |

|----------------------|-----------------|-----|-------|

| Minimum Pattern Data | 150°C           | 10  | Years |

| Retention Time       | 125°C           | 20  | Years |

### DC CHARACTERISTICS - CMOS COMPATIBLE

$(Vcc = 3.3V, Vss = 0V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                              | Symbol | Conditions                                                                              |         | Min | Тур        | Max  | Unit |

|--------------------------------------------------------|--------|-----------------------------------------------------------------------------------------|---------|-----|------------|------|------|

| Input Leakage Current                                  | Li     | Vcc = 3.6, VIN = GND                                                                    |         |     | 10         | μΑ   |      |

| Output Leakage Current                                 | ILOx32 | Vcc = 3.6, VIN = GND                                                                    | or Vcc  |     |            | 10   | μA   |

| Vcc Active Current for Read (1)                        | Icc1   | CS = VIL, OE = VIH, f =                                                                 | 5MHz    |     |            | 65   | mA   |

| Vcc Active Current for Program or Erase (2)            | Icc2   | CS = VIL, OE = VIH                                                                      |         |     |            | 120  | mA   |

| Vcc Standby Current                                    | Іссз   | Vcc = 3.6, CS = ViH, f                                                                  | = 5MHz  |     |            | 20   | mA   |

| Vcc Reset Current (2)                                  | Icc4   | RESET = Vss ± 0.3V                                                                      |         |     | 1          | 20   | mA   |

| Automatic Sleep Mode (2,4)                             | Icc5   | V <sub>IH</sub> = V <sub>CC ±</sub> 0.3 V;<br>V <sub>IL</sub> = V <sub>SS ±</sub> 0.3 V |         | 1   | 20         | mA   |      |

| Vcc Active Read-While-Program Current (1,2)            | Icc6   | CE = VIL, OE = VIH                                                                      | Word    |     | 85         | 180  | mA   |

| Vcc Active Program-While-Erase<br>Current (1,2)        | Icc7   | CE = VIL, OE = VIH                                                                      | Word    |     | 85         | 180  | mA   |

| Vcc Active Program-While-Erase-Suspended Current (2,5) | Icc8   | CE = VIL, OE = VIH                                                                      |         |     | 70         | 140  | mA   |

| Acc Accelerated Program Current                        | IACC   |                                                                                         | Acc Pin |     | 20         | 40   |      |

|                                                        |        | CE = VIL, OE = VIH                                                                      | Vcc Pin |     | 60         | 120  | mA   |

| Output Low Voltage                                     | Vol    | IoL = 5.8  mA, Vcc = 3                                                                  | 3.0     |     |            | 0.45 | V    |

| Output High Voltage                                    | Vон1   | Iон = -2.0 mA, Vcc =                                                                    | 3.0     |     | 0.85 x Vcc |      | V    |

| Low Vcc Lock-Out Voltage (4)                           | VLKO   |                                                                                         |         | 2.3 |            | 2.5  | V    |

#### NOTES

- 1. The Icc current listed includes both the DC operating current and the frequency dependent component (at 5 MHz). The frequency component typically is less than 8 mA/MHz, with OE at Viii.

- 2.Icc active while Embedded Algorithm (program or erase) is in progress.

- 3.DC test conditions: VIL = 0.3V, VIH = Vcc 0.3V

- 4. Guaranteed by design, but not tested.

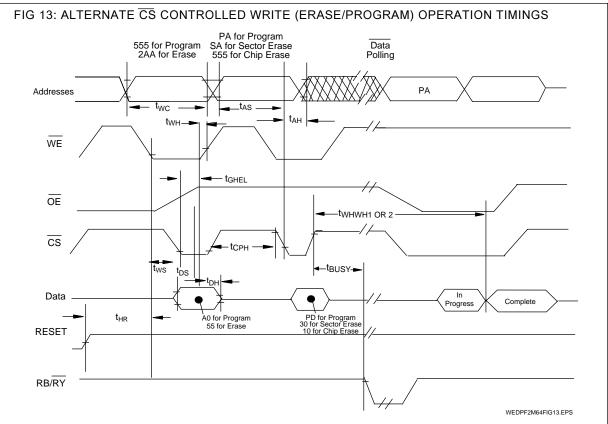

# AC CHARACTERISTICS-WRITE/ERASE/PROGRAM OPERATIONS, CS CONTROLLED

$(Vcc = 3.3V, Vss = 0V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                  | Symbol | Symbol |     | <u>-70</u> |     | <u>-100</u> |     | <u>-120</u> |     | <u>-150</u> |     |

|--------------------------------------------|--------|--------|-----|------------|-----|-------------|-----|-------------|-----|-------------|-----|

|                                            |        |        | Min | Max        | Min | Max         | Min | Max         | Min | Max         |     |

| Write Cycle Time                           | tavav  | twc    | 70  |            | 100 |             | 120 |             | 150 |             | ns  |

| Write Enable Setup Time                    | twlel  | tws    | 0   |            | 0   |             | 0   |             | 0   |             | ns  |

| Chip Select Pulse Width                    | telen  | tcp    | 35  |            | 45  |             | 50  |             | 50  |             | ns  |

| Address Setup Time                         | tavel  | tas    | 0   |            | 0   |             | 0   |             | 0   |             | ns  |

| Data Setup Time                            | toveh  | tos    | 45  |            | 45  |             | 50  |             | 50  |             | ns  |

| Data Hold Time                             | tendx  | tон    | 0   |            | 0   |             | 0   |             | 0   |             | ns  |

| Address Hold Time                          | tELAX  | tah    | 45  |            | 45  |             | 50  |             | 50  |             | ns  |

| Chip Select Pulse Width High               | tehel  | tсрн   | 30  |            | 30  |             | 30  |             | 30  |             | ns  |

| Duration of Byte Programming Operation (1) | twnwh1 |        |     | 300        |     | 300         |     | 300         |     | 300         | μs  |

| Sector Erase Time                          | twhwh2 |        |     | 15         |     | 15          |     | 15          |     | 15          | sec |

| Read Recovery Time (2)                     | tGHEL  |        | 0   |            | 0   |             | 0   |             | 0   |             | μs  |

| Chip Programming Time                      |        |        |     | 50         |     | 50          |     | 50          |     | 50          | sec |

- 1. Typical value for twhwh1 is 9µs.

- 2. Guaranteed by design, but not tested.

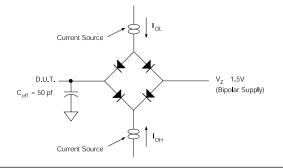

# FIG 2: AC TEST CIRCUIT

### **ACTEST CONDITIONS**

| Parameter                        | Тур                | Unit |

|----------------------------------|--------------------|------|

| Input Pulse Levels               | VIL = 0, VIH = 2.5 | ٧    |

| Input Rise and Fall              | 5                  | ns   |

| Input and Output Reference Level | 1.5                | V    |

| Output Timing Reference Level    | 1.5                | ٧    |

#### NOTES:

Vz is programmable from -2V to +7V. Io. & IoH programmable from 0 to 16mA. Tester Impedance  $Z_0 = 75\Omega$ .

Vz is typically the midpoint of VoH and Vol.

lot & loh are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

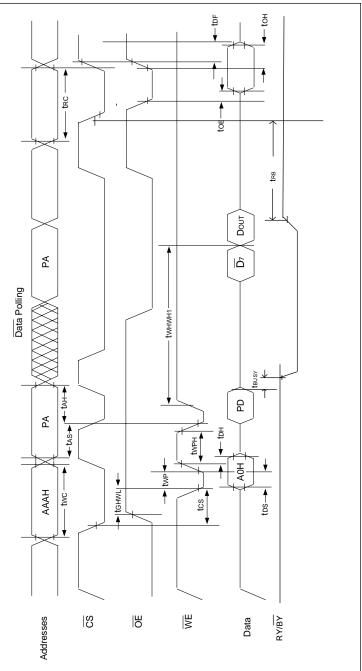

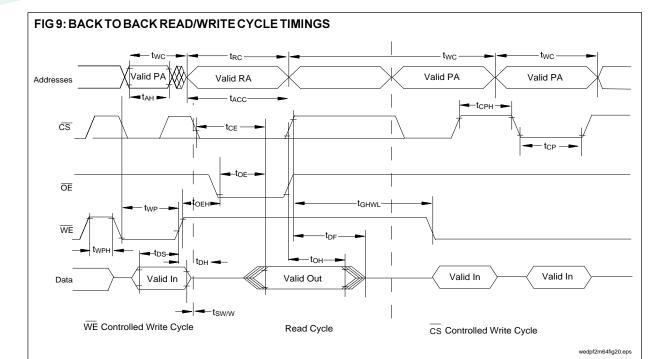

# AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS - WE CONTROLLED

$(Vcc = 3.3V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                              | Sym    | bol   | <u> </u> | <u>70</u> | 1   | 00  | <u>-1</u> : | 20  | <u>-150</u> |     | Unit |

|--------------------------------------------------------|--------|-------|----------|-----------|-----|-----|-------------|-----|-------------|-----|------|

|                                                        |        |       | Min      | Max       | Min | Max | Min         | Max | Min         | Max |      |

| Write Cycle Time                                       | tAVAV  | tWC   | 70       |           | 100 |     | 120         |     | 150         |     | ns   |

| Chip Select Setup Time                                 | tELWL  | tCS   | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Write Enable Pulse Width                               | tWLWH  | tWP   | 35       |           | 50  |     | 50          |     | 65          |     | ns   |

| Address Setup Time                                     | tAVWL  | tAS   | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Data Setup Time                                        | tDVWH  | tDS   | 45       |           | 50  |     | 50          |     | 65          |     | ns   |

| Data Hold Time                                         | tWHDX  | tDH   | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Address Hold Time                                      | tWLAX  | tAH   | 45       |           | 50  |     | 50          |     | 65          |     | ns   |

| Write Enable Pulse Width High                          | tWHWL  | tWPH  | 30       |           | 30  |     | 30          |     | 35          |     | ns   |

| Duration of Byte Programming Operation (1)             | tWHWH1 |       |          | 300       | 300 |     | 300         |     |             | 300 | μs   |

| Sector Erase                                           | tWHWH2 |       |          | 15        | 15  |     | 15          |     |             | 15  | sec  |

| Read Recovery Time before Write (3)                    | tGHWL  |       | 0        |           | 0   |     | 0           |     | 0           |     | μs   |

| VCC Setup Time                                         | tVCS   |       | 50       |           | 50  |     | 50          |     | 50          |     | μs   |

| Chip Programming Time                                  |        |       |          | 50        |     | 50  |             | 50  |             | 50  | sec  |

| Output Enable Setup Time                               |        | tOES  | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Output Enable Hold Time (2)                            |        | tOEH  | 10       |           | 10  |     | 10          |     | 10          |     | ns   |

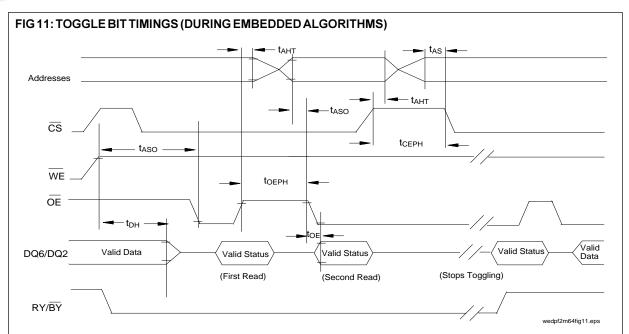

| Address Setup Time to OE low during toggle bit polling |        | tASO  | 15       |           | 15  |     | 15          |     | 15          |     | ns   |

| Address Hold Time From CS or OE high during toggle     |        | tAHT  | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Output Enable High during toggle bit polling           |        | tOEPH | 20       |           | 20  |     | 20          |     | 20          |     | ns   |

| Latency Between Read and Write Operations              |        | tsr/W | 0        |           | 0   |     | 0           |     | 0           |     | n s  |

| Write Recovery Time from RY/BY                         |        | tRB   | 0        |           | 0   |     | 0           |     | 0           |     | ns   |

| Program/Erase Valis to RY/BY                           |        | tBUSY | 90       |           | 90  |     | 90          |     | 90          |     | ns   |

- 1. Typical value for twhwh1 is 9µs.

- 2. For Toggle and Data Polling.

- 3. Guaranteed by design, but not tested.

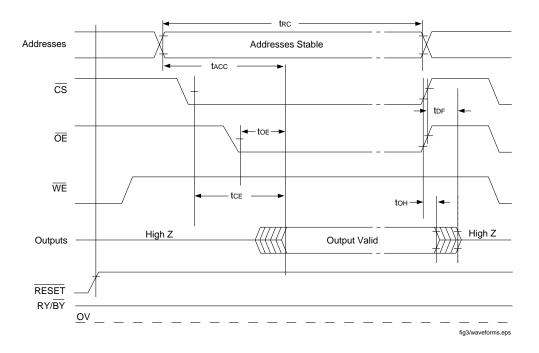

# AC CHARACTERISTICS - READ-ONLY OPERATIONS

$(Vcc = 3.3V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                             |                 | Sym   | Symbol |     | <u>-70</u> |     | <u>-100</u> |     | <u>-120</u> |     | <u>-150</u> |    |

|---------------------------------------|-----------------|-------|--------|-----|------------|-----|-------------|-----|-------------|-----|-------------|----|

|                                       |                 |       |        | Min | Max        | Min | Max         | Min | Max         | Min | Max         |    |

| Read Cycle Time                       |                 | tAVAV | tRC    | 70  |            | 100 |             | 120 |             | 150 |             | ns |

| Address Access Time                   |                 | tAVQV | tACC   |     | 70         |     | 100         |     | 120         |     | 150         | ns |

| Chip Select Access Time               |                 | tELQV | tCE    |     | 70         |     | 100         |     | 120         |     | 150         | ns |

| Output Enable to Output Valid         |                 | tGLQV | tOE    |     | 40         |     | 40          |     | 50          |     | 55          | ns |

| Chip Select High to Output High Z (1) |                 | tEHQZ | tDF    |     | 30         |     | 30          |     | 30          |     | 40          | ns |

| Output Enable High to Output H        | igh Z (1)       | tGHQZ | tDF    |     | 30         |     | 30          |     | 30          |     | 40          | ns |

| Output Hold from Addresses, C         | S or OE Change, | tAXQX | tOH    | 0   |            |     | 0           |     | 0           |     |             | ns |

| Whichever is first                    |                 |       |        |     |            |     |             |     |             |     |             |    |

|                                       | Read            |       | tOEH   | 0   |            | 0   |             | 0   |             | 0   |             |    |

| Output Enable Hold Time (1)           | Toggle and      |       |        |     |            |     |             |     |             |     |             |    |

|                                       | Data Polling    |       |        | 10  |            | 10  |             | 10  |             | 10  |             |    |

<sup>1.</sup> Guaranteed by design, not tested.

# FIG 3: AC WAVEFORMS FOR READ OPERATIONS

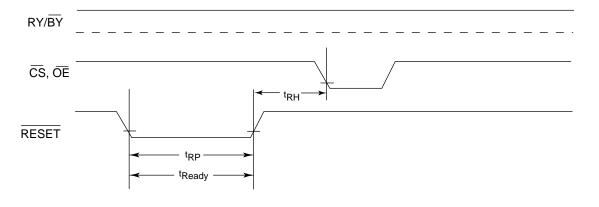

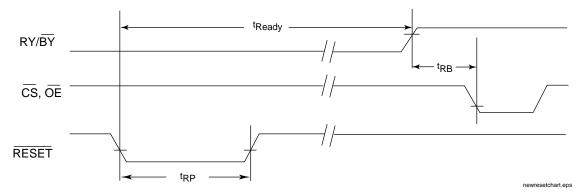

# AC CHARACTERISTICS - HARDWARE RESET (RESET)

| Parameter                                                              | Symbol |  | <u>-1</u> | 00  | <u>-1</u> | 20  | <u>-1</u> | <u>50</u> | Unit |

|------------------------------------------------------------------------|--------|--|-----------|-----|-----------|-----|-----------|-----------|------|

|                                                                        |        |  | Min       | Max | Min       | Max | Min       | Max       |      |

| RESET Pin Low (During Embedded Algorithms) to Read Mode (See Note)     | tready |  |           | 20  |           | 20  |           | 20        | μs   |

| RESET Pin Low (NOT During Embedded Algorithms) to Read Mode (See Note) | tready |  |           | 500 |           | 500 |           | 500       | ns   |

| RESET Pulse Width                                                      | trp    |  | 500       |     | 500       |     | 500       |           | ns   |

| RESET High Time Before Read (See Note)                                 | tкн    |  | 50        |     | 50        |     | 50        |           | ns   |

| RESET Low to Standby Mode                                              | trpd   |  | 20        |     | 20        |     | 20        |           | μs   |

| RY/BY Recovery Time                                                    | trв    |  | 0         |     | 0         |     | 0         |           | ns   |

Note: Not 100% tested.

### FIG 4: RESET TIMINGS NOT DURING EMBEDDED ALGORITHMS

# FIG 5: RESET TIMINGS DURING EMBEDDED ALGORITHMS

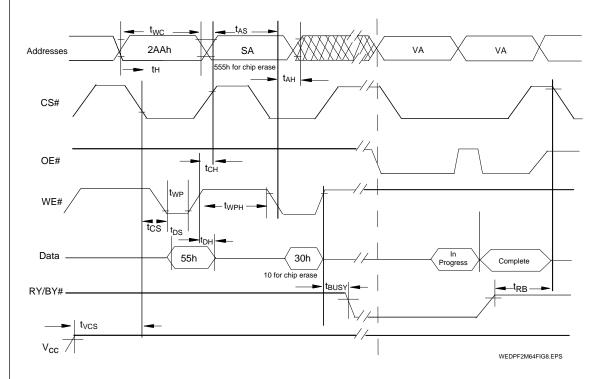

# FIG 6: WRITE/ERASE/PROGRAM OPERATION, WE CONTROLLED

#### NOTES:

- 1. PA is the address of the memory location to be programmed.

- 2. PD is the data to be programmed at byte address.

- 3.  $\overline{D}_7$  is the output of the complement of the data written to each chip.

- 4. Dout is the output of the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

# FIG 8: CHIP/SECTOR ERASE OPERATION TIMINGS

### NOTES:

1. SA = sector address (for Sector Erase), VA = Valid Address for reading status data (see "Write Operation Status").

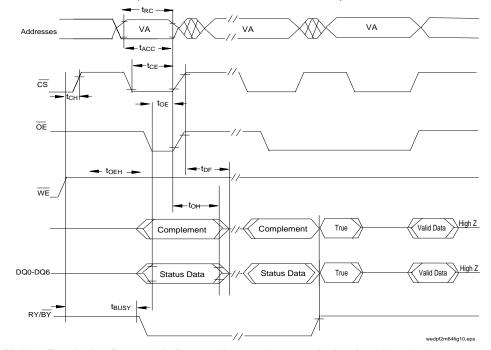

# FIG. 10: DATA POLLING TIMINGS (DURING EMBEDDED ALGORITHMS)

NOTE: VA = Valid address. Illustration shows first status cycle after command sequence, last status read cycle, and array data read cycle.

NOTE: VA = Valid address, not required for DQ6. Illustration shows first two status cycle after comand sequence, last status read cycle, and array data read cycle.

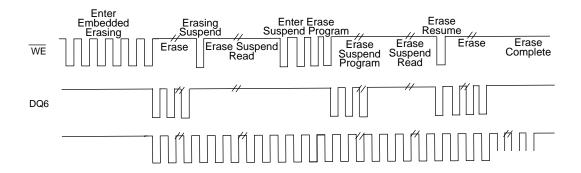

### FIG 12: DQ2 VS. DQ6

NOTE: DQ2 toggles only when read at an address within an erase-suspended sector. The system may use  $\overline{\text{OE}}$  or  $\overline{\text{CS}}$ .

### NOTES:

- 1. Figure indicates last two bus cycles of a program or erase operation.

- 2. PA = program address, SA = sector address, PD = program data.

- 3. DQ7 is the complement of the data written to the device. D<sub>OUT</sub> is the data written to the device.

ALL LINEAR DIMENSIONS ARE IN MILLIMETERS AND PARENTHETICALLY IN INCHES

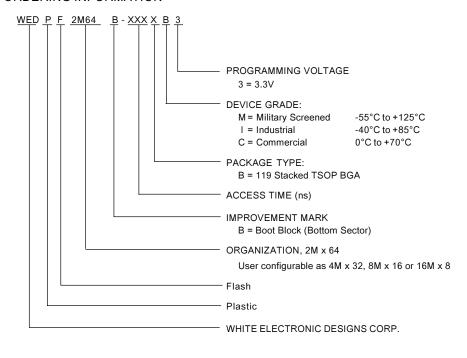

### ORDERING INFORMATION